4. 使用SignalTap II嵌入式逻辑分析仪在线调试¶

前面的每个工程我们都做了RTL仿真,可以很大概率保证我们设计的代码功能是没问题的,但是这并不能保证万无一失,因为我们最终的目的是要求综合后的程序下载到硬件系统后正常工作。万一我们把做了RTL仿真的综合后的代码下载到硬件系统中不能正常工作(越在高速系统中越常见),我们该怎么办呢?这时就可以使出我们的杀 手锏武器——嵌入式逻辑分析仪。本节我们就给大家详细说说为什么要用嵌入式逻辑分析仪,它可以做什么,什么情况下使用,基于什么样的原理,以及它的使用方法。

4.1. 逻辑分析仪简介¶

我们先来介绍下什么是逻辑分析仪。逻辑分析仪是不同于示波器的另一种用于调试的仪器,虽然有些示波器也带有逻辑分析仪的功能,但是不如专门的逻辑分析仪功能更强大。逻辑分析仪是分析数字系统逻辑关系的仪器。逻辑分析仪是属于数据域测试仪器中的一种总线分析仪,即以总线概念为基础,同时对多条数据线上的数据流进行观察和 测试的仪器,这种仪器对复杂的数字系统的测试和分析十分有效。逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器 ,最主要作用在于时序判定。由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1和0),因此设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与 Low之间形成数字波形。所以用这种仪器来调试FPGA最适合不过了。

图 79‑1

我们使用逻辑分析仪所作的调试也称为在线调试或板级调试,它是将综合后的程序下载到 FPGA 芯片后分析代码运行的情况。在实际情况中,有以下情况我们需要用到在线调试:

(1)仿真不全面而没有发现的 FPGA 设计错误。很多情况下,由于太复杂,无法做到 100%的代码覆盖率。

(2)在板级交互中,存在异步事件,很难做仿真,或者仿真起来时间很长,无法运行。

(3)除了本身 FPGA 外,还可能存在板上互连可靠性问题、电源问题和 IC 之间的信号干扰问题,都可能导致系统运行出错。

(4)其他潜在问题。

在线调试的方式主要有两种,一种是利用外部测试设备,把内部信号传送到FPGA 针脚上,然后用示波器或者逻辑分析仪观察信号;另一种就是利用嵌入式逻辑分析仪,在设计中插入逻辑分析仪,利用 JTAG 边缘数据扫描和开发工具完成数据交互。

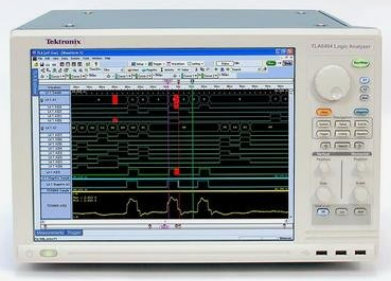

嵌入式逻辑分析仪的原理相当与在 FPGA中开辟一个存储器,存储器的大小决定了能够查看的数据的深度(多少),可以人为设定,但是不得超出 FPGA 所含有的逻辑资源(这也是嵌入式逻辑分析仪的一个缺点)。在 FPGA 内部,根据设置的采样时钟和需要查看的信号节点,对数据进行采样,并放置到设定的存储空间里,存储空间内容随时间更新。然后通过判断触发点来检查采集数据,一旦满足触发条件,这个时候会停止扫描,然后将触发点前后的一些数据返回给PC 端的测试工具进行波形显示,供开发者进行调试。目前的在线调试工具基本都是和对应的 FPGA 开发平台挂钩,不同 FPGA厂商都会有自己的软件开发平台,嵌入式逻辑分析仪也就不同。Quartus软件中的嵌入式逻辑分析仪叫SignalTap II,全称SignalTap II Logic Analyzer,是第二代系统级调试工具,可以捕获和显示实时信号,是一款功能强大且极具实用性的FPGA片上调试工具软件。

下面对比下两种分析仪的特点。

外部逻辑分析仪:传统的外部逻辑分析仪在测试复杂的 FPGA 设计时,会面临如下一些问题:

(1)缺少空余 I/O 引脚。设计中器件的选择依据设计规模而定,通常所选器件的 I/O 引脚数目和设计的需求是恰好匹配的。

(2)I/O 引脚难以引出。设计者为减小电路板的面积,大都采用细间距工艺技术,在不改变 PCB 板布线的情况下引出 I/O 引脚非常困难。

(3)外接逻辑分析仪有改变 FPGA 设计中信号原来状态的可能,因此难以保证信号的正确性。

(4)传统的逻辑分析仪价格昂贵,将会加重设计方的经济负担。

图 79‑2

嵌入式逻辑分析仪:Quartus软件的嵌入式逻辑分析仪SignalTap II基本上采用了典型外部逻辑分析仪的理念和功能,却无需额外的逻辑分析设备、测试 I/O、电路板走线和探点,只要建立一个对应的.stp文件并做相关设置后,与当前工程捆绑编译,用一根 JTAG 接口的下载电缆连接到要调试的FPGA 器件即可。SignalTap II对 FPGA 的引脚和内部的连线信号进行捕获后,将数据存储在一定的 RAM 块中。因此,用于保存采样时钟信号和被捕获的待测信号的 RAM 块,也会占用逻辑资源(LE)、Memory 资源(Block RAM)和布线资源。占用逻辑资源的多少基于信号或者被监测的通道数量,以及触发条件的复杂程度;所使用的存储器数量取决于被监测的通道数量和采样深度。

图 79‑3

4.2. SignalTap II的使用¶

我们用串口rs232工程作为例子来学习SignalTap II的使用,在SignalTap II中设置好采样的时钟、深度、要抓取的信号和触发条件,然后将综合后的程序下载到开发板中,使用PC端的串口调试助手发送数据,最后在SignalTap II中观察波形。详细步骤如下:

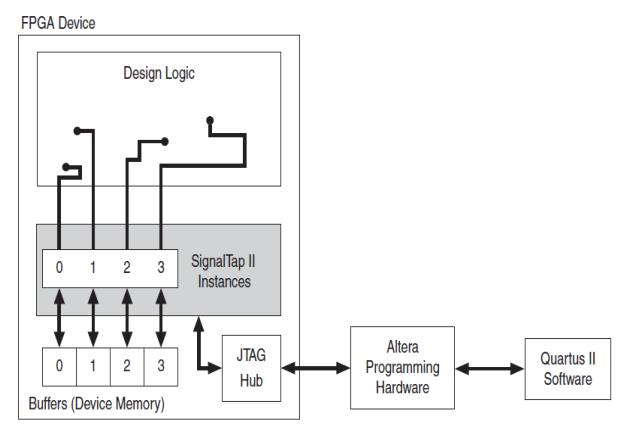

如图 79‑4所示为用Quartus 软件打开rs232工程。

图 79‑4

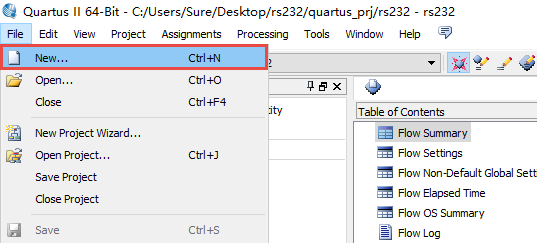

如图 79‑5所示,在打开的工程界面中点击“File”下的“New…”。

图 79‑5

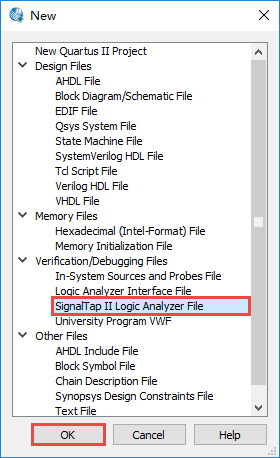

如图 79‑6所示,在该界面中我们可以选择新建各种相关的文件,这里我们选择“SignalTap II Logic Analyzer Files”即新建一个SignalTap II(.stp)文件,然后点击“OK”。

图 79‑6

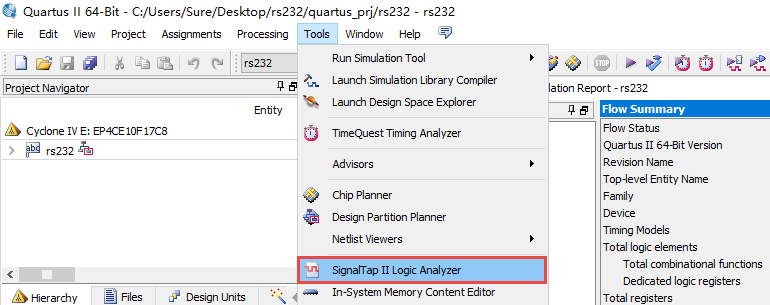

如图 79‑7所示,我们也可以直接点击“Tools”下的“SignalTap II Logic Analyzer”即可快速新建一个SignalTap II(.stp)文件。

图 79‑7

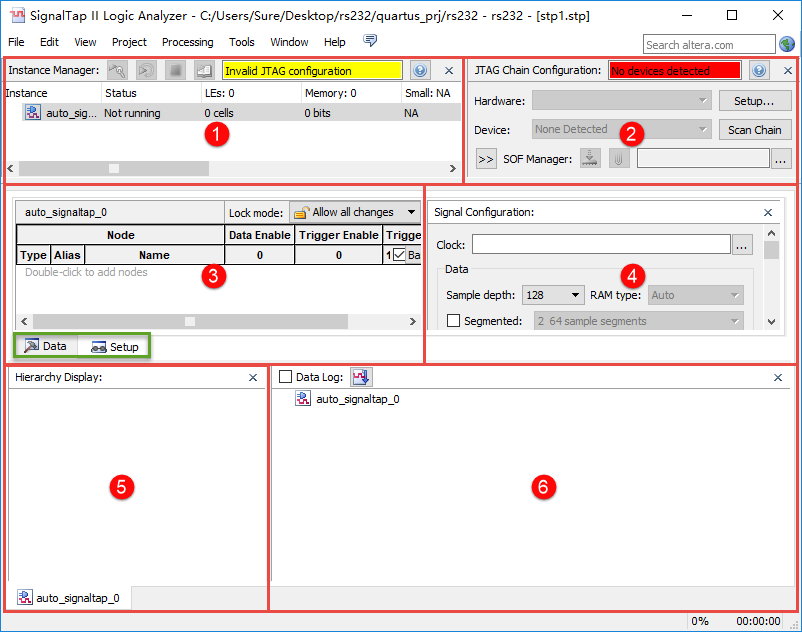

如图 79‑8所示,为新打开的SignalTap Ⅱ窗口。其中:

红色框 1 为 渐进式编译选项面板,实例管理器在每个器件中逻辑分析仪的多个嵌入式实例上建立并进行 SignalTap II 逻辑分析。可以使用它在 SignalTap II 文件中对单独和独特的逻辑分析仪实例建立、删除、重命名、应用设置。实例管理器显示当前 SignalTap II 文件中的所有实例、每个相关实例的当前状态以及相关实例中使用的逻辑单元和存储器比特的数量。实例管理器可以协助检查每个逻辑分析仪在器件上要求的资源使用量。可以选择多个逻辑分析仪并选择 Run Analysis(Processing 菜单)来同时启动多个逻辑分析仪。

红色框2为JTAG链配置面板,用于下载加入在线逻辑分析仪后的程序。

红色框 3为视图切换面板,该区域可以通过绿色框所示的位置切换不同的视图显示,其中“Data”视图用来观察实时采到的波形,“Setup”视图用来选择添加需要观察的信号和设置触发条件。

红色框 4为信号配置面板,用于设置采样时钟、设置采样方式、设置触发方式等。

红色框 5为分层设计面板,显示该工程的设计层次。

红色框 6为设计日志面板,所有在线调试的相关信息都会在此处打印出来。

图 79‑8

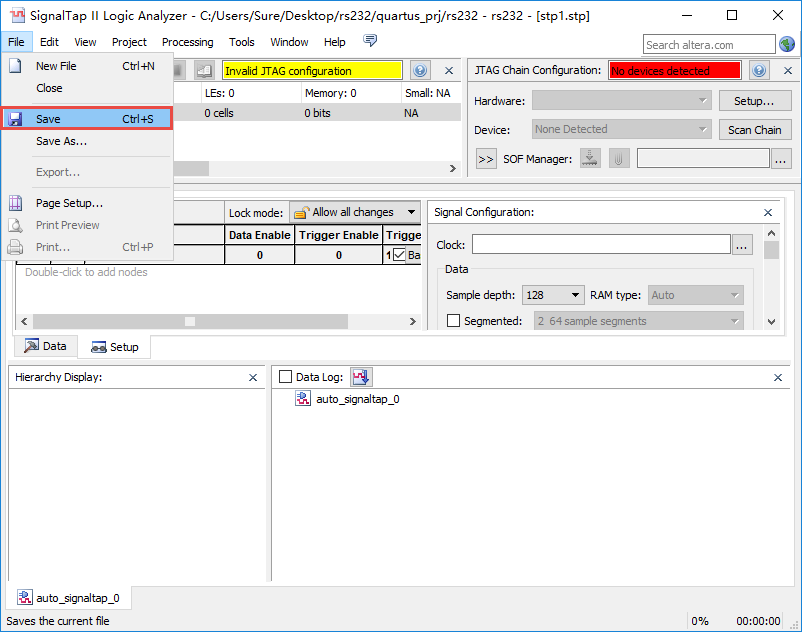

与其他文件一样,SignalTap II 文件也需要保存。如图 79‑9所示,选择“File” 下的“Save as”。

图 79‑9

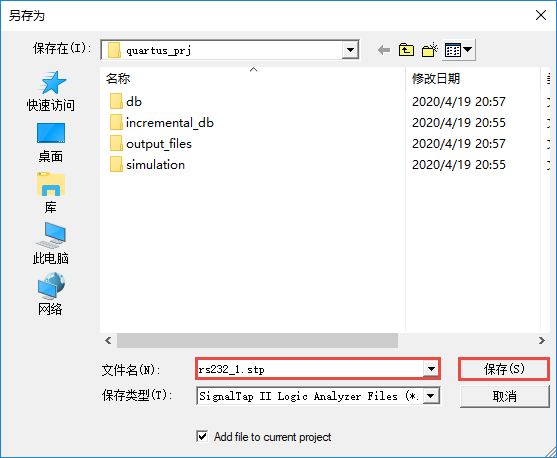

如图 79‑10所示,保存路径已经定位到当前工程目录下了,因为同一工程可以建立多个SignalTap II 文件,所以输入此 SignalTap II 文件名为“rs232_1.stp”,然后点击“保存(S)”

图 79‑10

如图 79‑11所示,提示没有数据和触发对话框,点击“OK”。

图 79‑11

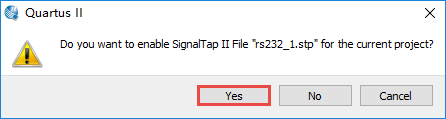

如图 79‑12所示,提示是否在当前工程中使能名为“rs232_1.stp”的SignalTap II 文件,点击“Yes”同意再次编译时将此 SignalTap II 文件与工程捆绑在一起综合、适配,以便共同下载进 FPGA 芯片中实现实时测试。

图 79‑12

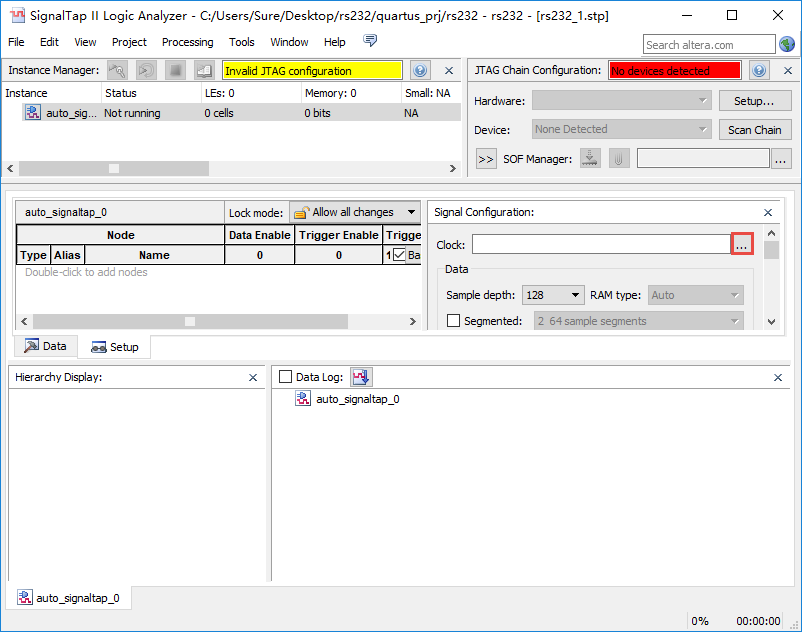

点击如图 79‑13所示的位置,在信号配置面板中首先添加采样时钟,采样时钟的频率越高,采集的数据点就越密集。

图 79‑13

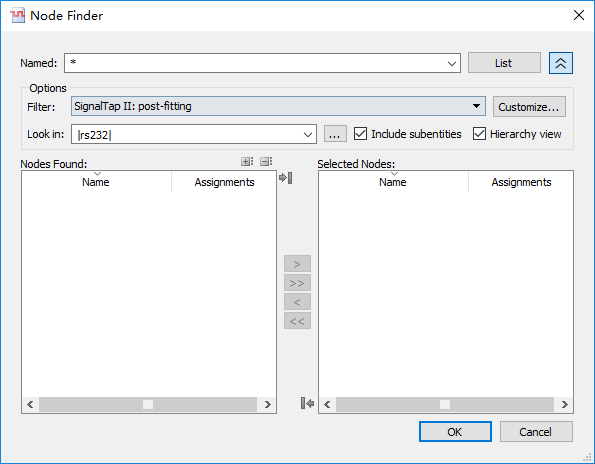

开发板上采用的是 50MHz 的晶振,在引脚分配时已经将它作为输入的时钟信号 sys_clk,我们把它作为采样时钟。如图 79‑14所示,在弹出的 Node Finder 对话框(在添加需要观察的信号时还会用到该对话框)。“ Named:”、“Filter:” 和“ Look in:”这三个选项用于精确查找我们所要添加的信号。

“Named :”是通过信号名称筛选信号,默认为通配符“*”,表示跳过名称筛选。如果我们需要添加sys_clk则可以在该选项框中输入“syc_clk”,该功能可以快速准确定位到你所需要的信号。

图 79‑14

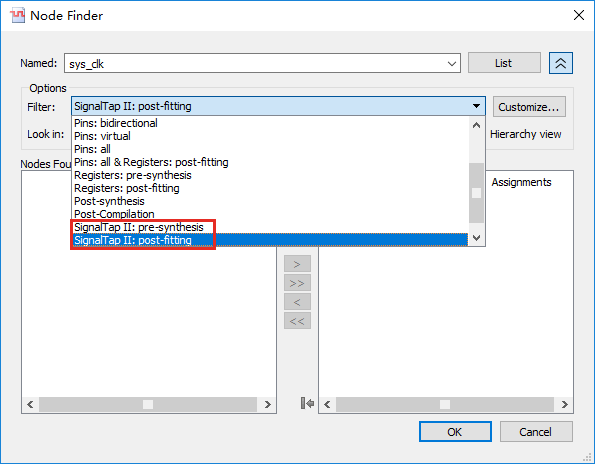

“Filter:” 是根据信号类型来过滤我们所需要的信号,常用的有 “pre-synthesis” 和“post-fitting”,如图 79‑15所示,其中 “pre-synthesis” 代表综合前设计中的信号,与 Verilog 设计中存在的信号最为接近,用于选择RTL级的信号;而“ post-fitting” 用于选择综合优化、布局布线之后的一些信号,与设计电路的物理结构最为接近。“pre-synthesis ”并不能筛选出到所有信号节点,但寄存器端口和组合逻辑端口可以被提取到,但大部分情况下我们使用 “pre-synthesis ”已经足够。

图 79‑15

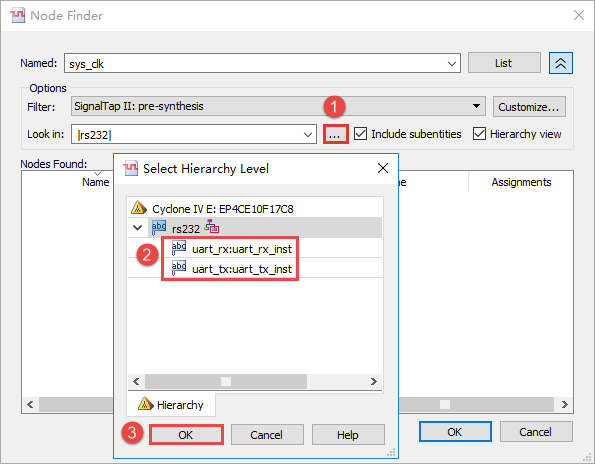

“Look in: ”可以将信号筛选锁定在某个层次和模块进行。点击如图 79‑16所示①处的图标进入Select Hierarchy Level对话框界面,可以选择②处其他层次的模块,选择其他层次的模块后点击③处的“OK”即可。该功能在一个复杂的工程包含多个不同层次的模块非常有用,能够帮助我们快速锁定信号所在的层次和模块,然后再去寻找具体的信号。

图 79‑16

在本章的学习中我们将系统时钟sys_ clk作为采样时钟,如图 79‑17所示,根据序号顺序,在①处的“Named :”选项框中输入“sys_ clk”,点击 ②处的“List”,在③处的“Node Found :”列表中就会列出名为sys_clk 的信号,双击③处的sys_clk信号或点击图标④,sys_clk信号就被添加到⑤处的“Selected Nodes:”中了。如果我们想取消⑤处选择的信号则在“Selected Nodes:”选中该信号后点击图标⑥即可。设置完毕后点击“OK”退出。

图 79‑17

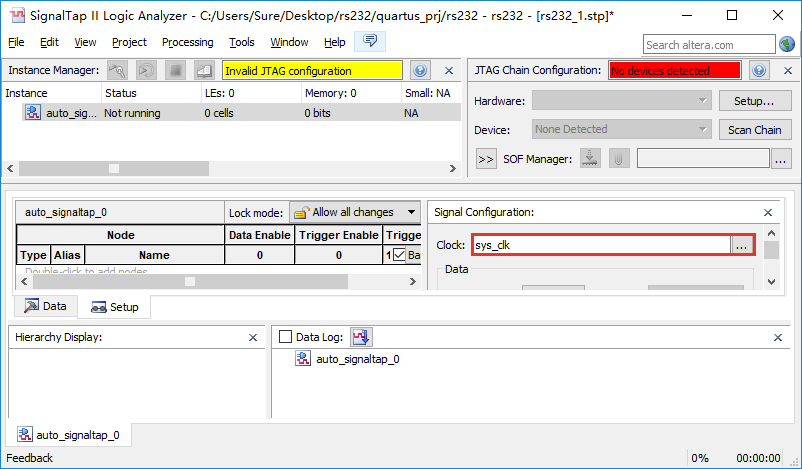

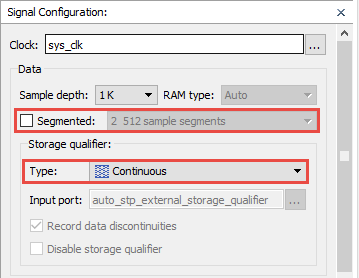

如图 79‑18所示,我们可以发现在“Clock:”栏中已经将采样时钟设置为sys_clk了。

图 79‑18

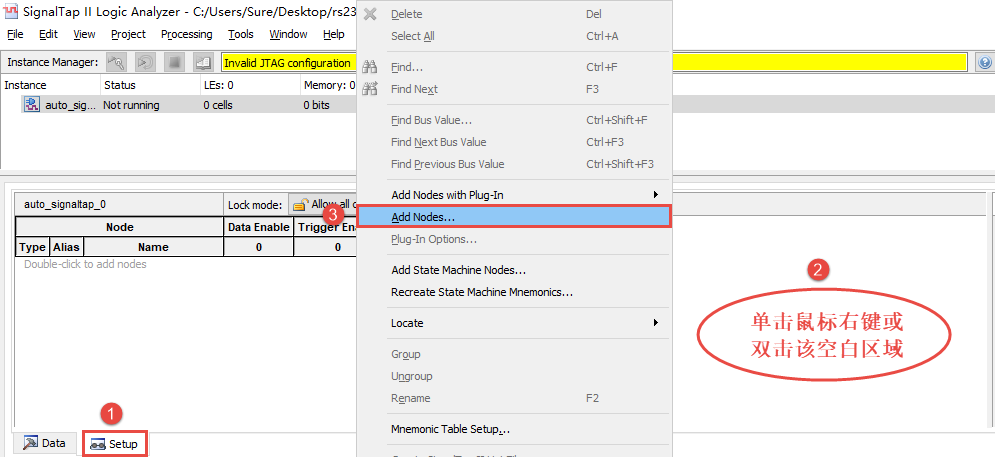

下面添加我们要观察的信号。如图 79‑19所示,在视图切换面板中选择①处的“Setup”标签页,在②处空白部分单击鼠标右键,选择③处的 “Add Nodes…”(也可以直接双击空白部分替换上述的两步操作)。

图 79‑19

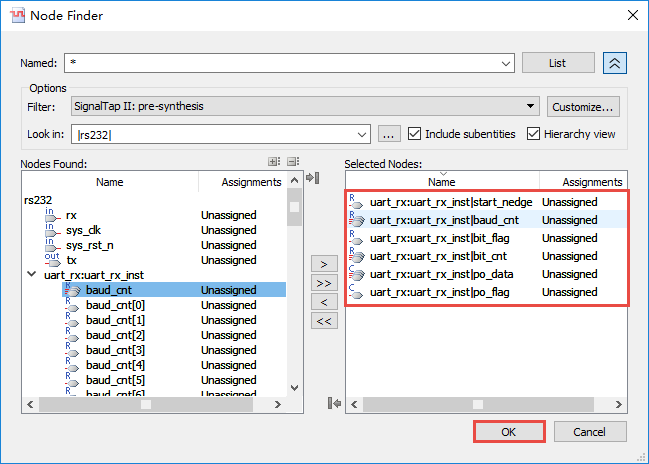

此时又弹出了Node Finder 对话框界面,我们仍然按照上面的方法选择我们需要的信号,这里我们选择如图 79‑20所示的信号进行观察,然后点击“OK”。

图 79‑20

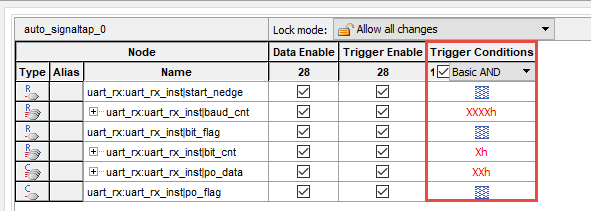

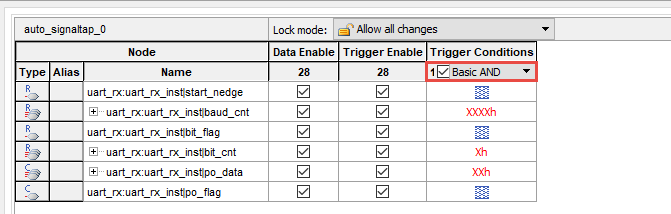

如图 79‑21所示,在视图切换面板中显示了已经添加要观察的信号,红色框内的触发条件我们还没有设置。

图 79‑21

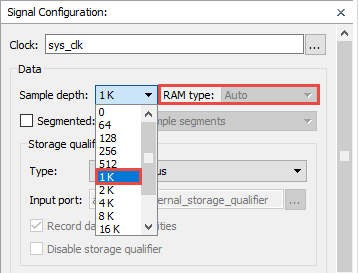

接下来设置采样方式。如图 79‑22所示,是设置采样深度,采样深度是设置需要多大的存储空间来显示波形(所占用的总存储空间=要观察的信号总位宽x设置的采样深度),设置的采样深度越大所占用的FPGA片上存储空间就越大,FPGA片上存储资源是有限的,也十分宝贵,如果我们的RTL设计已经占用了很多的FPGA 片上存储空间那么我们所要观察的信号个数和采样深度就会受到影响,所以不要一味的追求更深的采样深度,而是通过设置合理的触发条件来观察我们想要观察的信号节点的波形。采样深度的设置位于信号配置面板的 “Data ”栏中,点击“ Sample depth” 框右侧列表选择采样深度,这里我们选用1K的采样深度。“Sample depth ”框右侧还有一个“ RAM type:”框,通过 RAM 类型设置,用户可以选择使用哪一类型的存储器模块资源(例如M4K、M9K)来实现 SignalTap 存储器缓冲,从而防止使用到其他的存储器,避免对RTL设计的影响。但是这一设置只适用于有多种存储器模块类型的FPGA器件,对于不支持这一特性的器件,这一设置将被默认设置为AUTO并显示为灰色。 而我们使用的器件并不支持该特性,所以显示为灰色默认 AUTO。

图 79‑22

如图 79‑23所示,设置采样模式。采样模式分为分段采样和非分段采样(也叫循环采样),如果没有勾选上 “Segmented:”就是非分段采样,在信号触发后就连续采样至采样深度;如果勾选上了“Segmented:”,就是分段采样,将采样深度分为 N 段,信号每触发一次就采样一段长度的数据,需要连续触发 N 次采样才能至采样深度。“2 512 sample segments”代表将采样深度分成 2段,每段采样512个点。下面的“Type”类型设置,我们一般默认“Continuous” 即可。

图 79‑23

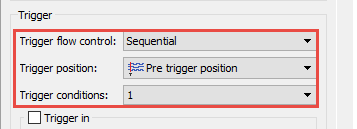

如图 79‑24所示,设置触发方式。触发方式的设置分为“Trigger flow control:”、“Trigger position:”和“Trigger conditions:”。

图 79‑24

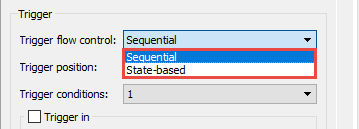

“Trigger flow control:”是触发流程控制的设置,如图 79‑25所示,分为“ Sequential”和 “State-based”两种,“State-based ”是基于状态的,用于较复杂的触发控制,对于一般的信号分析选择“ Sequential” 即可。

图 79‑25

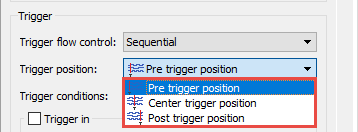

“Trigger position:”是触发位置的设置,如图 79‑26所示,为了更好的观察波形列表中可以选择触发位置前后数据的比例,“Pre trigger position:”是保存触发信号发生之前的信号状态信息(88%触发前数据,12%触发后数据);“Center trigger position:”保存触发信号发生前后的数据信息,各占 50%;“Post trigger position:”保存触发信号发生之后的信号状态信息(12%触发前数据,88%触发后数据)。

我们在“ Trigger position”触发位置设置中选择默认的“Pre trigger position”即可,也可以根据需求选择其他的设置。

图 79‑26

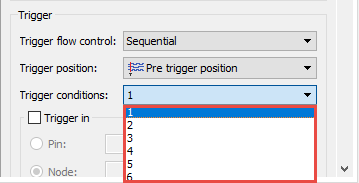

“Trigger conditions:”是触发条件的设置,如图 79‑27所示,触发条件选项可以选择触发条件的级别,最多可以设置 10 个触发级别。以“Sequential ”控制触发为例,对于多个级别的触发条件,如果非分段采样,则先等待判断 1 级触发条件是否满足,若满足则跳到触发条件 2 等待判断,否则继续等待,直到最后一级的触发条件判断满足后才正式开始捕获信号;对于分段采样,最后一级触发条件满足后开始捕获第一段信号,后面只需满足最后一级触发条件就再次捕获一段,也可以理解为前面级别的触发条件满足一次即可。大多数情况下1 个触发条件已经足够了,所以这里我们也选择1。

图 79‑27

如图 79‑28所示,触发条件的类型分为 “Basic” 和“Advanced”,我们选择默认的“ Basic ADN”即可。

图 79‑28

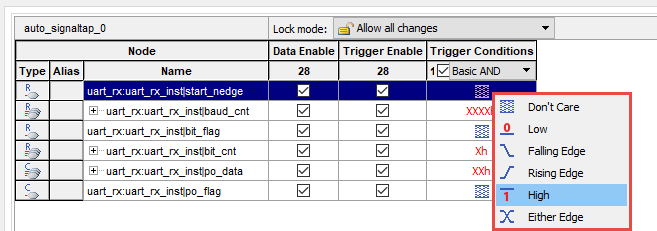

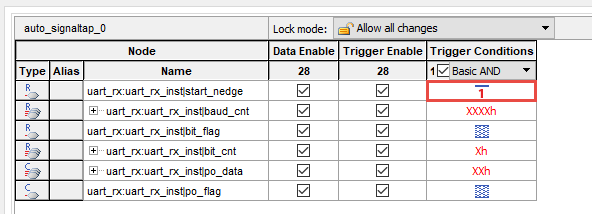

如图 79‑29所示,给要观察的信号设置触发条件,选中某个信号后右击弹出触发条件选择菜单,根据需求选择触发条件:“Don’t Care ”代表任意条件都触发,“Low” 表示信号低电平时触发,“Falling Edge”表示信号下降沿时触发,“Rising Edge ”表示信号上升沿时触发,“High” 表示信号高电平时触发,“Either Edge ”表示任意沿触发,如果是总线可以直接输入具体的值。同一列中的“Trigger Conditons ”属于同一级别,可以给该列中多个信号同时设置触发条件,但是要同时满足条件时才会触发,与触发条件级别的同时满足是有区别的。如图 79‑30所示,我们设置uart_rx模块中start_nedge下降沿标志信号的触发条件为高电平,当触发成功时在波形显示界面就可以捕获到波形。

图 79‑29

图 79‑30

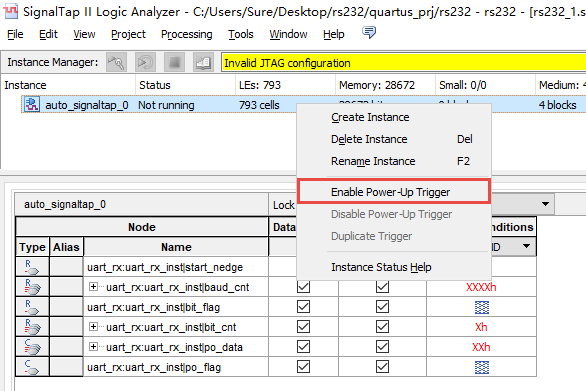

在使用SignalTap II 抓取信号时,经常会遇到有些信号只在开机后很短的时间内出现(比如几十us),如果按常规在开机运行后,再打开SignalTap II 抓取信号,此时需要抓取的信号已经过了,不能被抓取到,所所以SignalTap II里有一个“Power-Up Trigger”功能,可以在开机后就进行信号的捕获,这样只要是上电运行后的信号都能被抓取到。如图 79‑31所示,选中“auto_signaltap_0”后右击弹出菜单中选择“ Enable Power-Up Trigger”即可。

图 79‑31

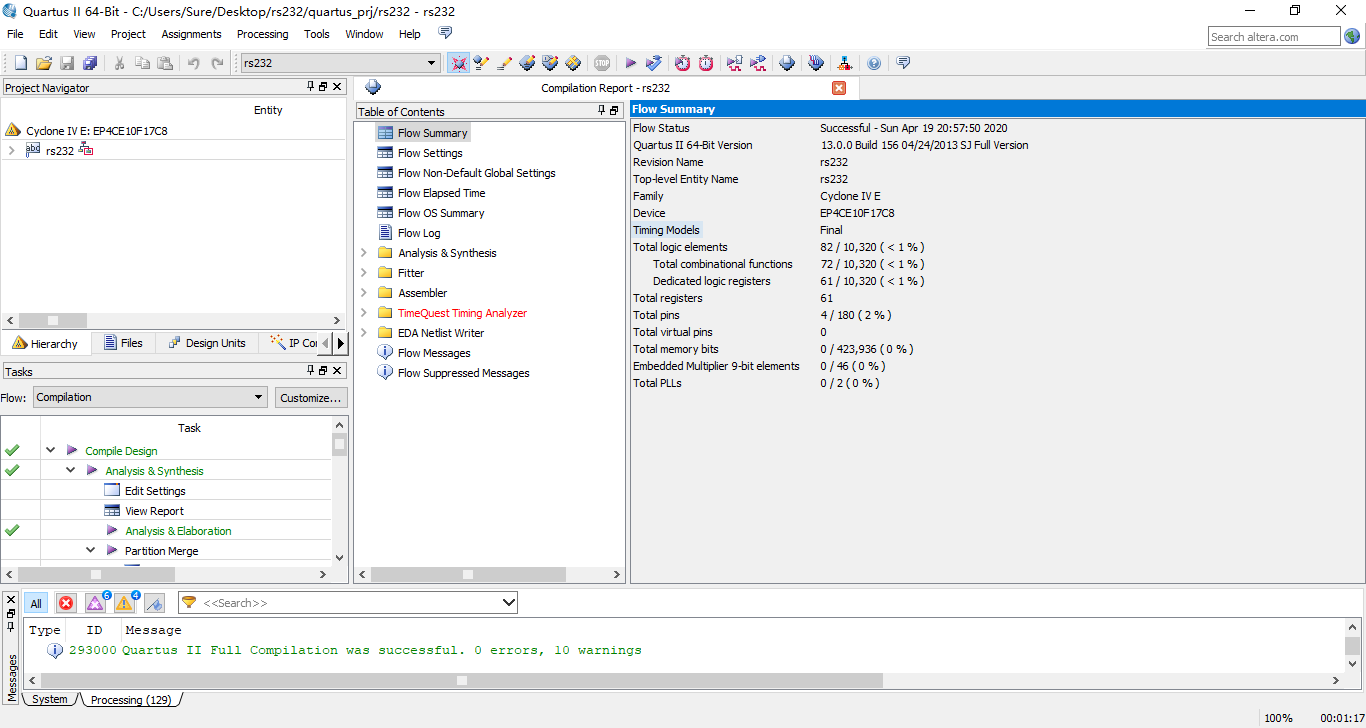

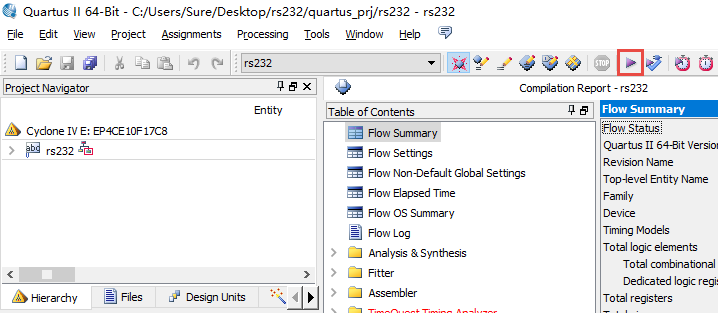

上述所有配置完成后一定要在工程界面中点击如图 79‑32所示的“Start Analysis & Synthesis”图标进行分析和综合才能将在线逻辑分析仪映射到FPGA中,然后将生成的新.sof文件下载到我们的开发板中进行在线调试。

图 79‑32

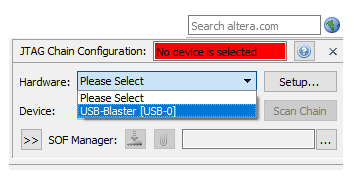

新的.sof文件生成后,将USB-Blaster下载器去开发板相连接;如图 79‑33所示,在Hardware 中选择对应的USB-Blaster[USB-0]。

图 79‑33

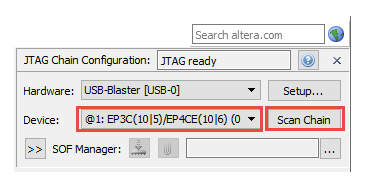

选择完毕后,可以看到刚才标红的内容变成了JTAG Ready,表示JTAG已经准备就绪,如图 79‑34所示。Device 一栏的内容也显示出来了(如果仍然没有发现 Device,可以点击右边的 Scan Chain搜索器件)。

图 79‑34

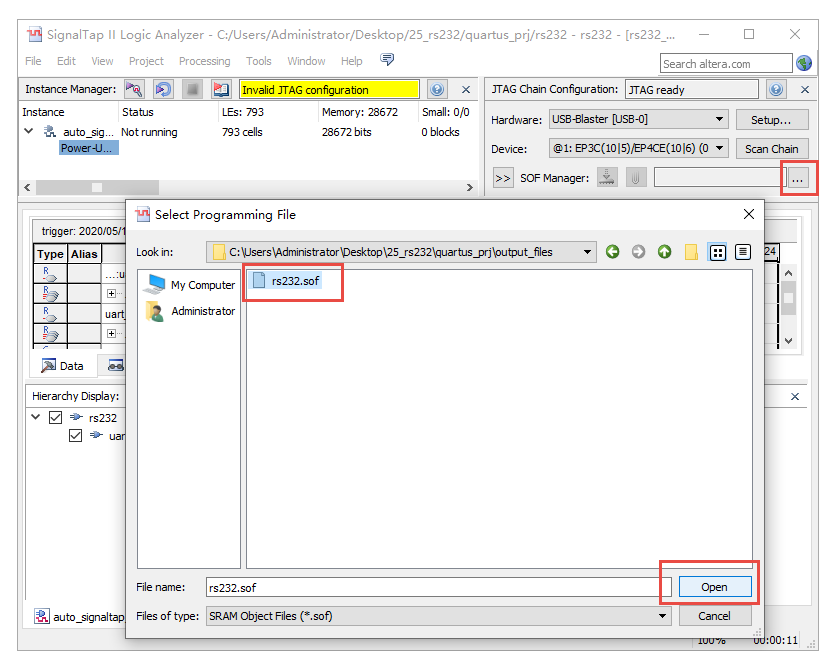

接下来是.sof文件的添加,如图 79‑35所示,点击“…”位置,找到我们要添加的sof文件,选择“open”。

图 79‑35

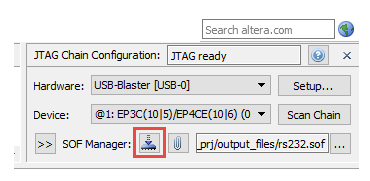

SOF文件选择完毕后,如图 79‑36所示,点击“Program Device”,将程序下载到开发板。

图 79‑36

SOF文件下载完成后,SignalTap II运行的准备工作就绪,我们回到控制区,如图 79‑37所示:①键是运行按钮,点击一次捕获一次信号;②键是连续运行按钮,点击一次捕获连续进行;③键是停止按钮,可以中止当前的信号捕获。Status栏显示着捕获状态,分为Not running(未运行)、Waiting for trigger(等待触发)和offloading acquired data(导出捕获到的数据),此时显示Not running,表示捕获未运行。

图 79‑37

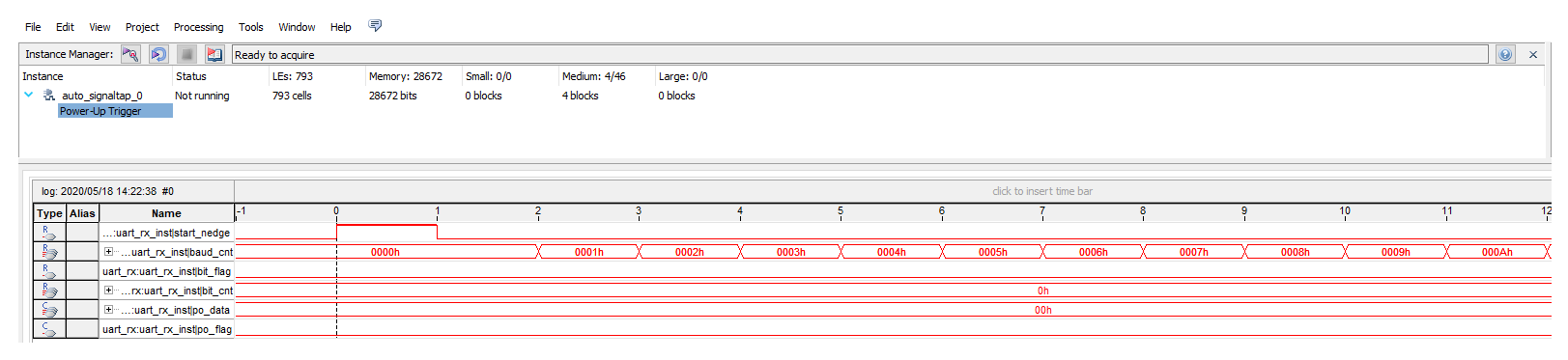

点击运行键,开始捕获信号,捕获完成后,设置区会自动切换到数据区,得到如图 79‑38、图 79‑39所示的数据。

图 79‑38

图 79‑39

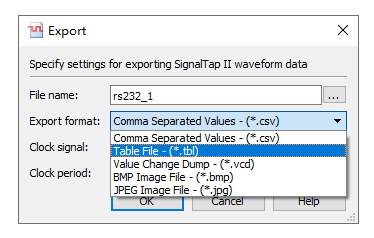

SignalTap II嵌入式逻辑分析仪可以采用矢量波形(.vwf)、矢量表(.tbl)、矢量文件(.vec)、逗号分割数据(.csv)和Verilog数值更改转存(.vcd) 文件格式输出所捕获的数据。这些文件格式可以被第三方验证工具读入,显示和分析SignalTap II嵌入式逻辑分析仪所捕获的数据。如图 79‑40、图 79‑41所示,点击“File”目录下的“export”,选择合适的文件类型,点击“ok”保存即可。

图 79‑40

图 79‑41

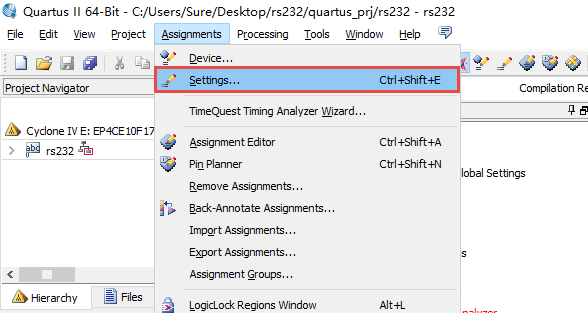

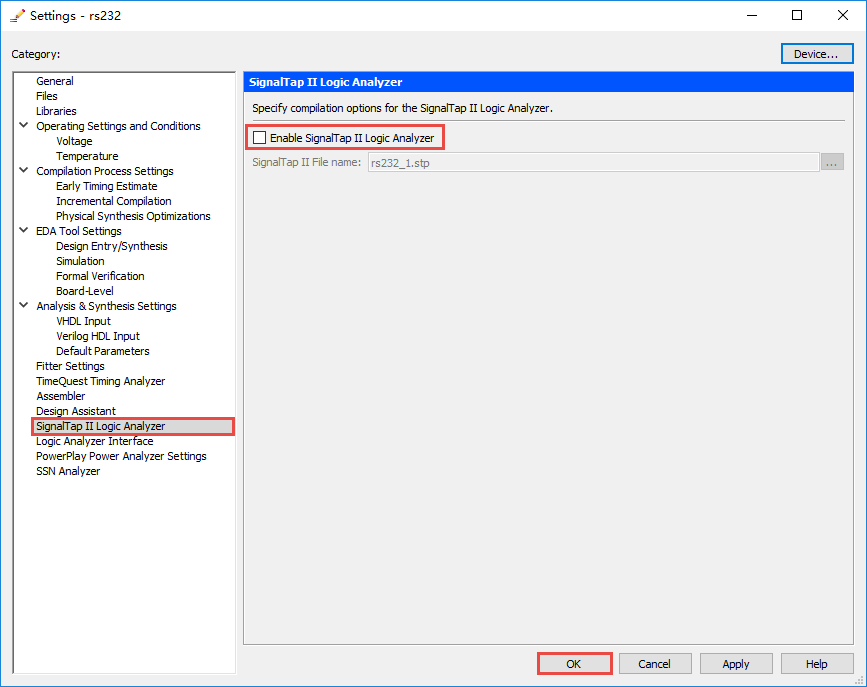

我们知道使用 SignalTap II 功能时会占用FPGA内部的资源,尤其是FPGA内部的存储器资源,所以我们在调试之后要将这部分资源释放掉,即在“Settings ”关闭 SignalTap II 功能。如图 79‑42所示,选择“Assignments”下的“Settings…”,在图 79‑43中选择“ SignalTap II Logic Analyzer”,我们可以看到在该界面中“Enable SignalTap II Logic Analyzer”前是打勾的,表示已经使能了下面的“rs232_1.stp”,我们只需要去掉这个勾即可关闭当前的在线逻辑分析仪功能,然后再次综合的时候就把在线逻辑分析仪所使用的资源给释放掉了,需要使用时再将其使能即可。

图 79‑42

图 79‑43