3. 硬件开发平台详解¶

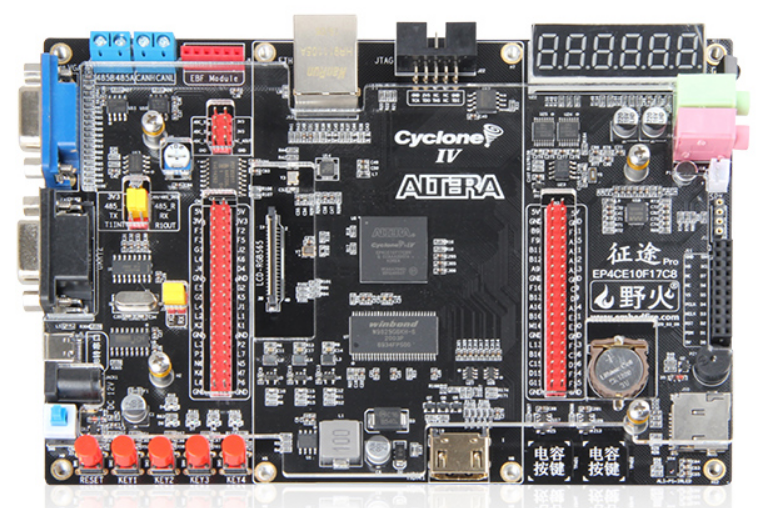

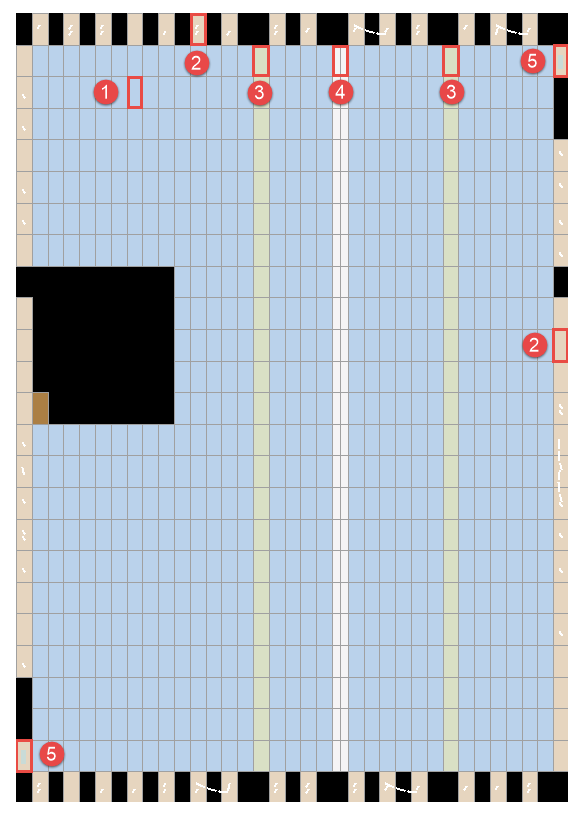

本书配套的硬件平台为:野火EP4CE10F17C8征途Pro FPGA开发板,本书所有的工程都是围绕该开发板进行设计讲解的,在学习的时候如果配套该硬件平台,那必然会达到事半功倍的效果。征途Pro 开发板的硬件资源,如图 3‑1所示。

图 3‑1 征途pro 开发板硬件资源图

如图 3‑1所示,可以看到征途pro 开发板的硬件资源是极为丰富的,下面我们分别为大家介绍各个硬件资源。

RS485接口

板载RS485总线接口,搭载的收发器为MAX3485芯片。通过485A和485B两个端口与外部RS485设备进行通信,通信时需将A口与A口,B口与B口连接,才能正常通信。

CAN接口

板载CAN通信总线接口,搭载的收发器为TJA1042芯片。通过CANH和CANL两个端口与外部CAN设备就行通信,同样的通信时需将H口与H口,L口与L口连接,才能正常通信。

EBF Module接口

自定义的外设接口,它可以连接野火部分配套的外设,比如OLED屏(I2C)。

AD/DA(模数/数模转换)

板载模数以及数模转换的AD/DA模块,搭载的芯片型号为PCF8591T。该芯片使用I2C总线与FPGA进行通信,使用该芯片可实现模拟信号与数字信号之间的转换。

以太网接口

板载网线接口(RJ45),搭载的PHY芯片型号为LAN8720A,使用RMII协议通信。我们可利用该芯片通过网线实现网络通信功能,通信速率可达100Mbps。

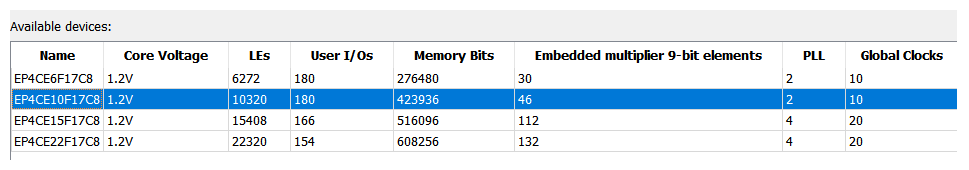

EP4CE10主芯片

该芯片为开发板的主芯片,即FPGA芯片,其型号为EP4CE10F17C8。该芯片拥有10k的逻辑单元,179个可配置的I/O口,414kbit的嵌入式RAM资源(每9kbit容量为一个块,每块为一个嵌入式存储单元,即有46个嵌入式存储单元),两个独立PLL锁相环,10个全局时钟网络。是一款性价比较高 的芯片。

下载接口(JTAG)

FPGA下载器通过该接口与开发板连接,用于程序的下载、固化以及调试。

SPI - FLASH

Flash存储器,芯片型号为W25Q16,存储容量为16Mbit。使用SPI协议实现FPGA芯片与Flash存储器的通信。Flash具有断电数据不丢失的特性,其作为FPGA芯片的上电配置器件,只要我们将程序存储在Flash中,FPGA上电后就能直接运行Flash中的程序,保证FPGA断电后程序不丢失 。

数码管

征途Pro 开发板上配置了六位八段数码管,同时搭载了两块74HC595芯片,74HC595具有串行输入,并行输出的功能。使用该芯片的四位控制信号即可输出14位的数码管控制信号,这样可以大大地节省IO口资源。

红外接收头

板载红外接收头,使用的接收头型号为HS0038B。同时我们还配套了一个红外遥控器用于实现遥控功能。

音频

一个音频输入接口(连接播放器),一个音频输出接口(连接耳机),搭载WM8978音频芯片。该音频芯片使用I2S总线传输音频数据,FPGA通过I2C总线对该芯片的寄存器进行配置。

咪头

板载咪头(MIC/麦克风),该接口连接到了WM8978音频芯片的录音输入端口,可用于接收录音数据。

喇叭接口

喇叭接口(XH2.0P),可通过该接口与喇叭进行连接,连接后可播放WM8978音频芯片输出的音频数据。

RTC时钟芯片

实时时钟芯片,芯片型号为PCF8563T,该芯片具有报警、时钟输出、定时等功能。FPGA芯片通过I2C总线与实时时钟芯片进行通信。

温湿度接口

该接口可用于连接DHT11(温湿度传感器)以及DS18B20(温度传感器)。FPGA芯片通过单总线与这两个器件进行通信。

摄像头接口

板载摄像头接口,支持野火OV7725/OV5640摄像头的连接使用。FPGA通过I2C总线进行对这两款摄像头进行配置。

蜂鸣器

板载蜂鸣器,这里我们使用的是有源蜂鸣器。该蜂鸣器在设计时可作为信息提示的发声器件。

TF卡座

板载TF卡座,该卡座用于插入Micro SD卡,插入SD卡后,FPGA可实现与SD卡的通信,例如可读取SD卡内的图片,音乐等。

环境光传感器

板载环境光传感器,芯片型号为AP3216C。FPFA通过I2C总线与该芯片进行通信,利用该芯片可检测环境光强。

RTC底座

板载RTC底座,该底座的型号为CR1220,用于放置供RTC使用的纽扣电池。

40P 排针*2

征途pro 开发板上配置了两个40Pin的排针接口,这些接口是开发板引出的扩展IO口,共引出80个扩展IO口。

电容式触摸按键

征途Pro 开发板上配置了两个电容式触摸按键。通过该按键可学习电容式按键的工作原理,同时在设计中电容按键还可以作为控制信号控制系统的运行。

HDMI接口

板载的HDMI接口(高清多媒体接口),该接口可与HDMI显示器相连接。开发板通过该接口发送需要显示的信息到HDMI显示器,从而达到高清显示。

SDRAM

板载SDRAM芯片,SDRAM是一个同步动态随机存储器。这里我们使用的SDRAM芯片型号为W9825G6KH-6,容量为256Mbit。在设计中其往往用于数据存储,如VGA显示中的图片存储,录音时的音频数据存储,摄像头HDMI显示中的图像存储等。

LCD接口

板载LCD接口,该接口可用于接入野火的RGB565 LCD显示屏,可用于图像格式为RGB565的图像显示,同时支持5点触控。FPGA芯片使用I2C总线对其进行触控驱动。

四个LED显示灯

板载四个led显示灯(蓝灯),这四个led灯可以作为程序的状态显示灯。可以设计通过led灯来判断程序是否正确执行,在调试时可以起到辅助作用。

复位按键

一个机械式的复位按键,用于程序的复位控制。

四个机械按键

征途pro 开发板上配置了丰富的按键资源,不仅有两个触摸按键和一个复位按键,还有四个机械按键。有了丰富的控制按键资源,这可以让我们的程序控制起来更为方便。

电源开关

在接入电源后,该开关可用于控制开发板的上电与断电。

电源输入(直流电源输入接口)

直流电源输入接口。可接入6V~12V的直流电源给开发板供电。

USB转串口

征途pro 开发板上配置了一个USB转串口的接口,可能有人会问为什么要配置这个接口,不是有串口接口了吗?那是因为现在的电脑上的串口接口正在被慢慢的摒弃,而笔记本上几乎就没有了这个接口。所以我们配置这个USB转串口的接口就可以让大家很方便的进行串口通信的调试。我们使用一根我们平时用的Tape C数据线,一端连接开发板,一端连接电脑即可进行调试。(在使用USB串口通信是必须将J2和J3的引脚用跳帽连接在一起,TXD和RX相连,RXD和TX相连。)

RS232接口(母头)

板载RS232接口(母头),公头一端连接外部串口设备(如电脑)。通过串口线实现FPGA与外部串口设备的通信。(使用时必需将J6的TX和T1INT,RX和R1OUT用跳帽连接。)

电位器接口

板载电位器,通过旋转电位器,可改变输入板载AD/DA芯片PCF8591T的A_IN0端口的模拟电压。

EEPROM

板载 EEPROM 芯片,容量为 64Kbit(8Kbyte)。 FPFA 通过 I2C 总线与该芯片进行通信,可读可写,掉电数据不丢失,可用于存储一些掉电不能丢失的重要数据,如系统配置参数。

VGA接口

板载VGA接口,该接口可与VGA显示器直接相连。相连后FPGA可通过VGA接口传输信息给VGA显示器进行显示。

3.1. 国内外FPGA产业现状¶

首先我们来说一下全球主要生产FPGA芯片的几大厂商,最被人们熟知的就是Xilinx和Altera两家巨头,紧排其后的就是Lattice公司。

Xilinx公司作为全球FPGA市场份额最大的公司,其发展动态往往也代表着整个FPGA行业的动态,Xilinx每年的都会在赛灵思开发者大会(XDF)上发布和提供一些新技术,很多FPGA领域的最新概念和应用往往也都是由Xilinx公司率先提出并实践,其高端系列的FPGA几乎达到了垄断的地位,是目前当之 无愧的FPGA业界老大,也是IC圈很知名的设计公司。

图 3‑2 Xilinx公司Logo

Altera公司于2015年被Intel斥资167亿美元收购,占全球FPGA市场份额第二。但是自从被Intel收购以后,似乎“Altera”这个品牌名就被雪藏了起来,不再提起了,但“Altera”的大名永远不会被历史遗忘。Intel将FPGA专注为自己的产业布局,并打造新属于自己的生态圈,在中高端F PGA领域也占有很重要地位。

图 3‑3 Altera公司Logo

Lattice公司以其低功耗产品著称,占全球FPGA市场份额第三,苹果7手机内部搭载的FPGA芯片就是Lattice公司的产品。Lattice公司是目前唯一一家在中国有研发部的外国FPGA厂商,也为国产FPGA厂商培养了很多业内优秀的管理人员和技术人员,当年国内企业欲收购Lattice,而被美国以违 反国家安全的名义否决了收购计划,使国产FPGA商业化还要走更长的路。

图 3‑4 Lattice公司Logo

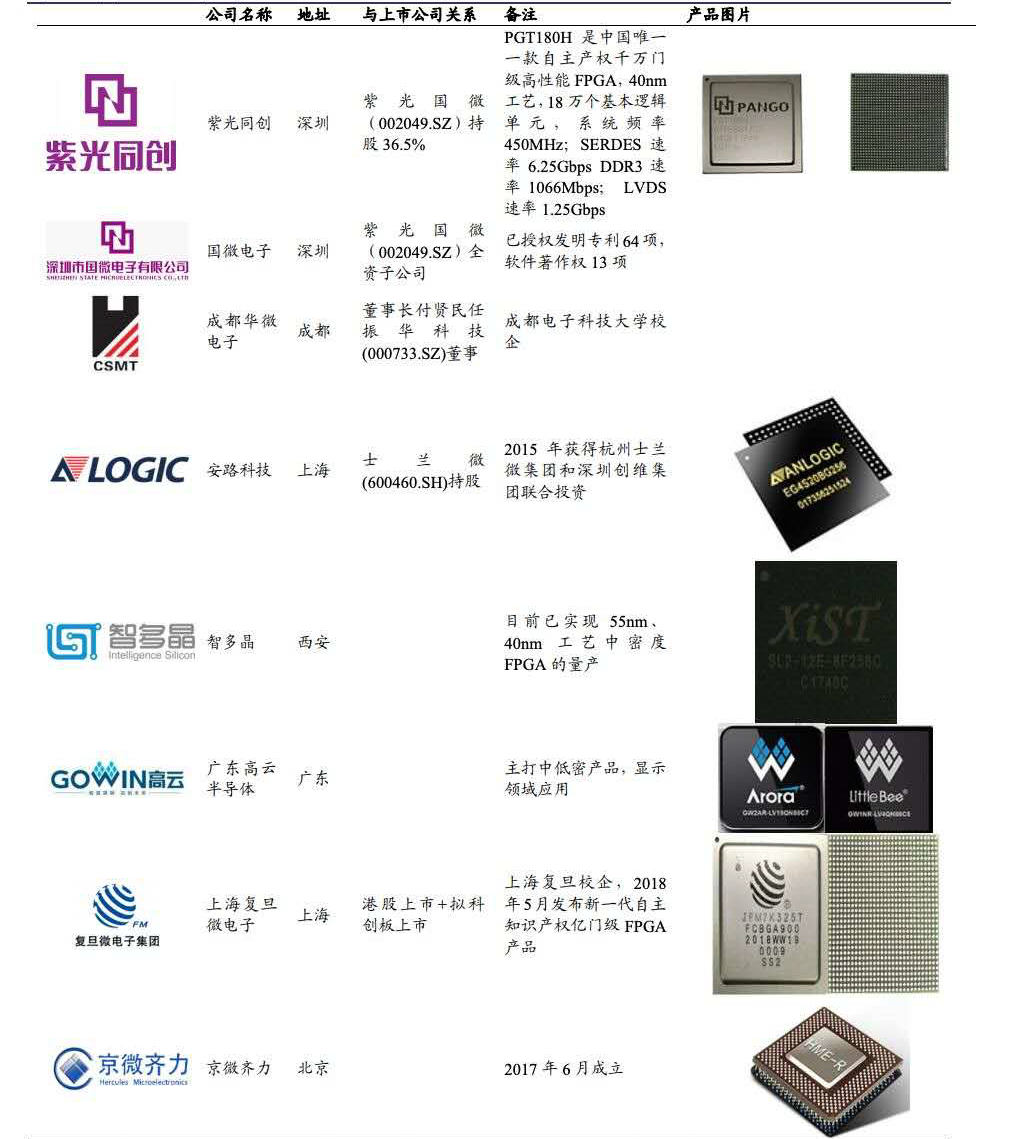

国外三巨头占据 90%全球市场,FPGA 市场呈现双寡头垄断格局,Xilinx 和Intel(Altera) 分别占据全球市场 56%和 31%,在中国 FPGA 市场中,占比也高达 52%和 28%,而目前国内厂商高端产品在硬件性能指标上均与上面三家FPGA巨头的高端产品有较大差距,国产FPGA厂商暂时落后。国产FPGA厂商目前在中国市场占比约 4%,未来随着国产厂商技术突破,FPGA 领域国产替代或将是百亿级的机会,替代空间广阔。国内 FPGA 厂商主要有 8 家:紫光同创、国微电子、成都华微电子、安路科技、智多晶、高云半导体、上海复旦微电子和京微齐力。目前营收规模均较小,国产FPGA 目前还处于起步期,专利数和国外企业有较大差距。产品角度来看,国产FPGA 在硬件性能指标上也远落后于 Xilinx 及Intel( Altera)。

图 3‑5 国内主要 FPGA 厂商

对于国产FPGA厂商来说,目前不少优秀国际人才的加盟给国产企业添加了新的活力。市场也给国产FPGA提供了千载难逢的机遇,国家政策在支持与倾斜,国内整体集成电路发展水平也在提升,因此现在正是国产FPGA厂商发展的良好机遇。

3.2. 我们选择CycloneIV的理由¶

了解了FPGA的国内外发展现状,读者肯定心存疑虑,为什么我们在选择FPGA芯片时,既没有选择使用市场份额占有量最大的Xilinx公司,也没有选择使用更具特色的Lattice公司,而是选择了Intel(Altera)公司的FPGA芯片呢?主要原因有以下几点:

Intel(Altera)FPGA芯片相对于Xilinx同量级的芯片价格更便宜,性价比更高;

Intel(Altrea)早年大学计划做的很好,入门资料相对较多;

Intel(Altera)的开发工具综合速度较快,软件也容易上手操作。

综上所述,我们选择Intel(Altera)公司的FPGA芯片开始FPGA的入门学习。

与Intel(Altera)公司相比,Xilinx公司在中高端领域芯片的开发和相关资料更加完善。也就是说,对于入门学习来讲,推荐使用Intel(Altera)公司的FPGA芯片;进阶提高的话,推荐使用Xilinx公司的FPGA芯片,而在实际的项目开发中,还需综合考虑成本、性能、开发周期等诸多因素。

Intel(Altea)公司在FPGA行业已深耕多年,已经建立了完备的FPGA芯片产业体系,针对应用场景的不同,设计并生产了诸多系列的FPGA芯片,分为MAX系列、Cyclone系列、Arria系列、Stratix系列和Agile系列。下面结合官方提供的说明进行简单介绍。详情请移步Intel官方网站 :

https://www.intel.cn/content/www/cn/zh/products/programmable/fpga.html

MAX系列:英特尔 MAX 10 FPGA 在低成本的瞬时接通小外形可编程逻辑设备中提供了先进的处理功能,能够革新非易失集成。它们提供支持模数转换器 (ADC) 的瞬时接通双配置,和特性齐全的 FPGA 功能,针对各种成本敏感性的大容量应用进行了优化,包括工业、汽车和通信等。除了MAX 10以外,该系列的其他产品都是CPLD。

图 3‑6 MAX系列

Cyclone系列:Cyclone FPGA 系列旨在满足用户的低功耗、低成本设计需求,支持用户加快产品上市速度。每一代 Cyclone FPGA 都可帮助用户解决技术挑战,以提高集成度、提升性能、降低功耗和缩短产品上市时间,同时满足用户的低成本要求。该系列芯片的定位为中低端,市场和教学中的应用最广泛。

图 3‑7 Cyclone系列

Arria系列:英特尔 Arria 设备家族可提供中端市场中的最佳性能和能效。英特尔 Arria设备家族拥有丰富的内存、逻辑和数字信号处理 (DSP) 模块特性集,以及高达 25.78 Gbps 收发器的卓越信号完整性,支持用户集成更多功能并最大限度地提高系统带宽。此外,Arria V 和英特尔 Arria 设备家族的 SoC 产品可提供基于 ARM 的硬核处理器系统 (HPS),从而进一步提高集成度和节省更多成本。该系列是性价比很高的一款产品。

图 3‑8 Arria系列

Stratix系列:英特尔 Stratix FPGA 和 SoC 系列结合了高密度、高性能和丰富的特性,可实现更多功能并最大程度地提高系统带宽,从而支持客户更快地向市场推出一流的高性能产品,并且降低风险。该系列属于高端高性能的FPGA。

图 3‑9 Stratix系列

Agile系列:英特尔 Agilex FPGA 家族采用异构 3D 系统级封装 (SiP) 技术,集成了英特尔首款基于 10 纳米制程技术的 FPGA 架构和第二代英特尔 Hyperflex FPGA 架构,可将性能提升多达 40%,将数据中心、网络和边缘计算应用的功耗降低多达 40%。英特尔Agilex SoC FPGA 还集成了四核 Arm Cortex-A53处理器,可提供高系统集成水平。该系列属于超高性能的SoC芯片,在高端应用场景中大放异彩。

图 3‑10 Agile系列

根据上面的介绍,考虑到价格、资源、性能以及学习资料的多样性,最适合作为入门学习的就是Cyclone系列的芯片了,而且Cyclone IV系列的芯片能够满足入门学习时所有的设计需求,价格比较便宜,FPGA入门之后,可以考虑入手高性能系列的FPGA芯片。

3.3. Cyclone系列FPGA芯片的命名方法¶

许多IC芯片表面都会有一行或多行由字母、数字组成的字符串,这就是芯片的“身份证”,用以表示芯片的相关信息,使用者可通过其了解芯片的生产厂家、产品系列、性能、容量等相关参数,FPGA也不例外。FPGA 生产厂商众多,不同厂商对自家产品都会有自己独特命名方式。前面说到,我们使用的是Intel(Altea)公司Cyclone系列的FPGA芯片,那自然要了解它的命名规则。

Cyclone系列FPGA芯片的命名规则如图 3‑11所示,名称信息的组成为:器件系列 + 器件类型(是否含有高速串行收发器) + LE逻辑单元数量 + 封装类型 + 高速串行收发器的数量(没有则不写) + 引脚数目 + 器件正常使用的温度范围 + 器件的速度等级 + 后缀。

图 3‑11 手册信息

以本开发板所使用的芯片EP4CE10F17C8N为例进行简单介绍:

EP4C:Altera器件Cyclone IV系列;

E/GX:E表示普通逻辑资源丰富的器件,GX表示带有高速串行收发器的器件;

10:LE逻辑单元的数量,单位为k,10表示约有10k的逻辑单元;

C:表示高速串行收发器的数量,该芯片没有高速串行收发器所以不写;

F:表示PCB封装类型,F是FBGA封装,E(EQFP)、Q(PQFP)、U(UBGA)、M(MBGA);

17:表示引脚数量,17代表有256个引脚;

C:工作温度,C表示可以工作在0℃到85℃(民用级),I表示可以工作在-40℃到100℃(工业级),A表示可以工作在-40℃到125℃(军用级);

8:器件的速度等级,6最大约是500MHz,7最大约是430MHz,8最大约是400MHz,可以看出在Altera的器件中数字越小表示速度越快,而在Xilinx的器件中数字越大表示速度越快;一般来讲,提高一个速度等级将带来12%到15%的性能提升,但是器件的成本却增加了20%大30%。如果利用设计结构来将性能提升12%到15%(通过增加额外的流水线),那么就可以降低速度等级,从而节约20%大30%的成本;

N:后缀,N表示无铅,ES代表工程样片。

3.4. fpga内部硬件结构简介¶

FPGA之所以能实现现场可编程是因为FPGA内部有很多可供用户任意配置的资源,其中包括:可编程逻辑阵列、可编程I/O、互连线、IP核等;学过数字电路的人都知道,使用与、或、非门的任意组合几乎可以实现所有的数字电路,但是FPGA内部最基本的主要单元并不是这些与、或、非门,而是由无数个查找表(Look Up Tabe,LUT)和寄存器构成。

初看FPGA内部结构,初学者只会觉得云里雾里,但了解FPGA的内部结构是有重要意义的。这能让我们了解在FPGA设计过程中,我们所编写的代码和硬件是怎样的一个映射关系,从而更加深入了解FPGA和单片机、ARM的区别。透彻了解了FPGA内部结构,才能对FPGA的设计了如指掌,这有助于进一步的系统优化,实 现低功耗、省资源、高稳定性的系统设计。

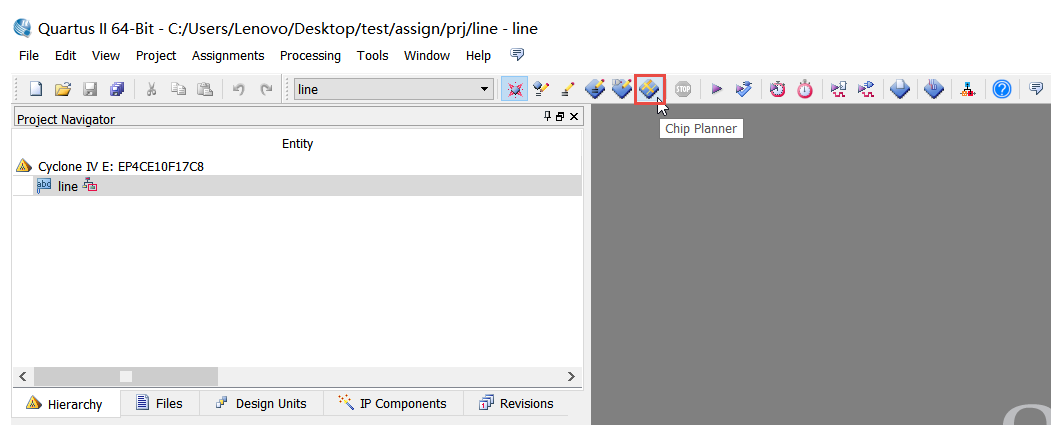

以本开发板使用的FPGA芯片进行介绍,其主要资源如图 3‑12所示(下面的演示可以等“Quartus软件和USB-Blaster驱动安装”章节学习完毕后再尝试操作):

图 3‑12 芯片主要资源

首先,我们来认识一下FPGA内部的诸多资源。点击图 3‑13所示图标打开“Chip Planner”来查看这款FPGA芯片的版图模型。

图 3‑13 打开版图模型

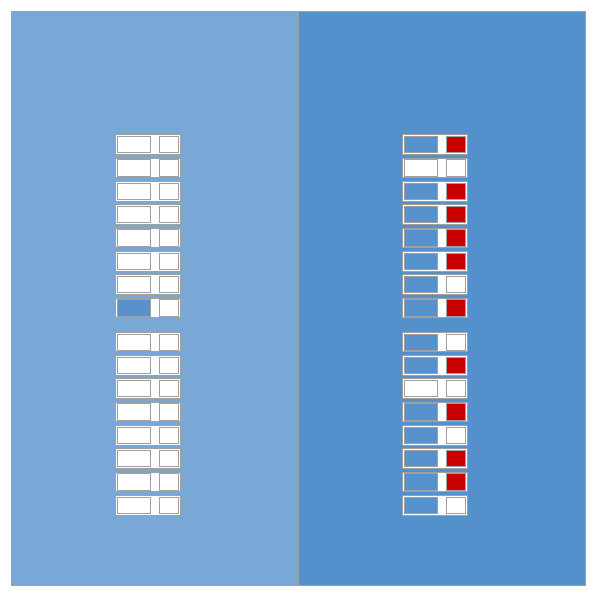

打开后的ChipPlanner视图如下所示,图 3‑14展示的是未进行布局布线的视图,片内资源未被使用,所以呈现浅色。图 3‑15是已经进行过布局布线操作后的视图,片内使用资源已映射到了版图模型(只有全编译后才能看到映射效果),其中深色表示该资源已经被使用,颜色越深的地方表示资源利用率越高;黑色区域为一些固定功能资源或无资源区域,用户不可对其进行任意配置。

图 3‑14 未进行布局布线操作的版图模型

图 3‑15 进行布局布线操作后的版图模型

逻辑阵列块(Logic Array Block,LAB):每个LAB由16个LE(Logic Element)组成,下图是两个已经映射资源后的LAB,资源利用率不同的LAB会有颜色差异(左边LAB使用资源量少,颜色较浅;右边LAB使用资源较多,颜色较深)。

图 3‑16 逻辑阵列块

放大后的LE如图 3‑17所示,每个LE主要由查找表(蓝色)和寄存器(红色)组成。整个芯片中共有10320个LE,约为10K,对应芯片型号“EP4CE10F17C8N”中的10。

图 3‑17 放大后的LE图

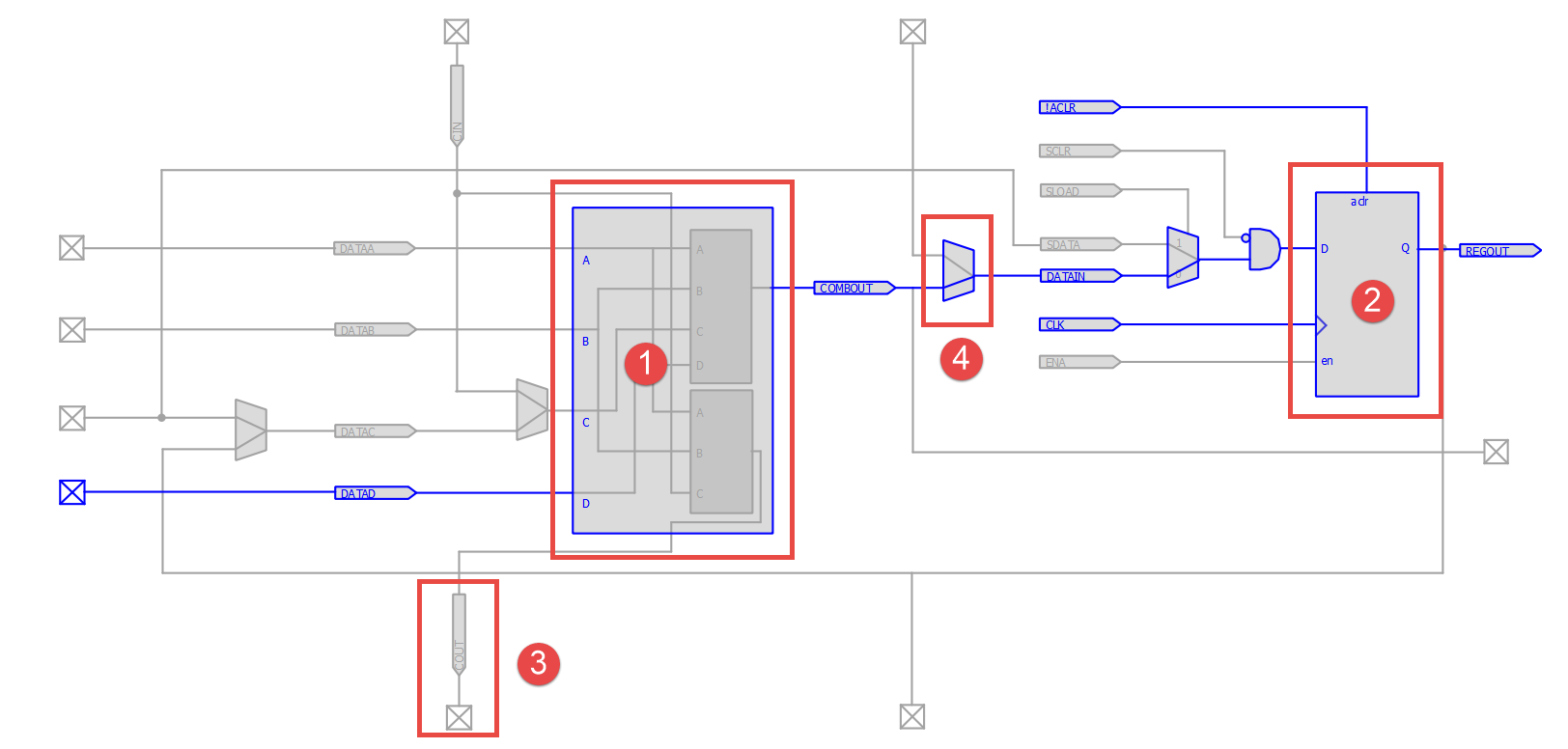

双击其中一个LE可以观察到其内部的大致结构(内部结构只有被使用才能够双击打开查看)。由图 3‑18可以看出,其结构主要分为两个部分:左侧为一个4输入的查找表;右侧为可编程寄存器;此外还包括数据选择器、进位链等。查找表和多路选择器完成组合逻辑功能,寄存器完成时序逻辑功能。(蓝色高亮的部分是已经使用的资源,未高亮灰色的部分是未被使用的资源)。

图 3‑18 LE内部结构图

这里的4输入查找表类似于一个容量为16 bits 的ROM(2^4 = 16)(工艺上是珍贵的 SRAM 资源),4表示地址输入位宽为 4 bits,查找表的存储内容作为输出结果与不同输入信号一一对应,在 FPGA 配置时载入。

标注①处为查找表:目前主流 FPGA 都采用了基于 SRAM 工艺的查找表结构。查找表本质上就是一个 RAM。当用户通过原理图或 HDL 语言描述设计出逻辑电路后,FPGA 开发软件会自动计算逻辑电路的所有可能结果,将其列成真值表的形式,并把真值表(即输入对应的输出逻辑)事先写入 RAM,这样每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。目前FPGA中多使用4输入的查找表,所以每一个查找表可以看成一个有4位地址线的RAM。

标注②处为寄存器:可以配置成多种工作方式,比如触发器或锁存器,同步复位或异步复位、复位高有效或低有效。

标注③处为进位链:超前进位加法器,方便加法器的实现,加快复杂加法的运算。

标注④处为数据选择器:数据选择器一般在 FPGA 配置后固定下来。

用户可编程I/O(User I/Os,也被简称为IOE):可编程I/O资源分布在整个芯片的四周。本芯片共有256个管脚,除去一些固定功能的管脚,可供用户任意配置的管脚资源只有180个,图 3‑19是其中一个可编程I/O单元,里面又包含三个最小单元(每个可编程I/O单元中的最小单元个数不固定,有的包含两个,也有的包含四个)。

图 3‑19 I/O资源图

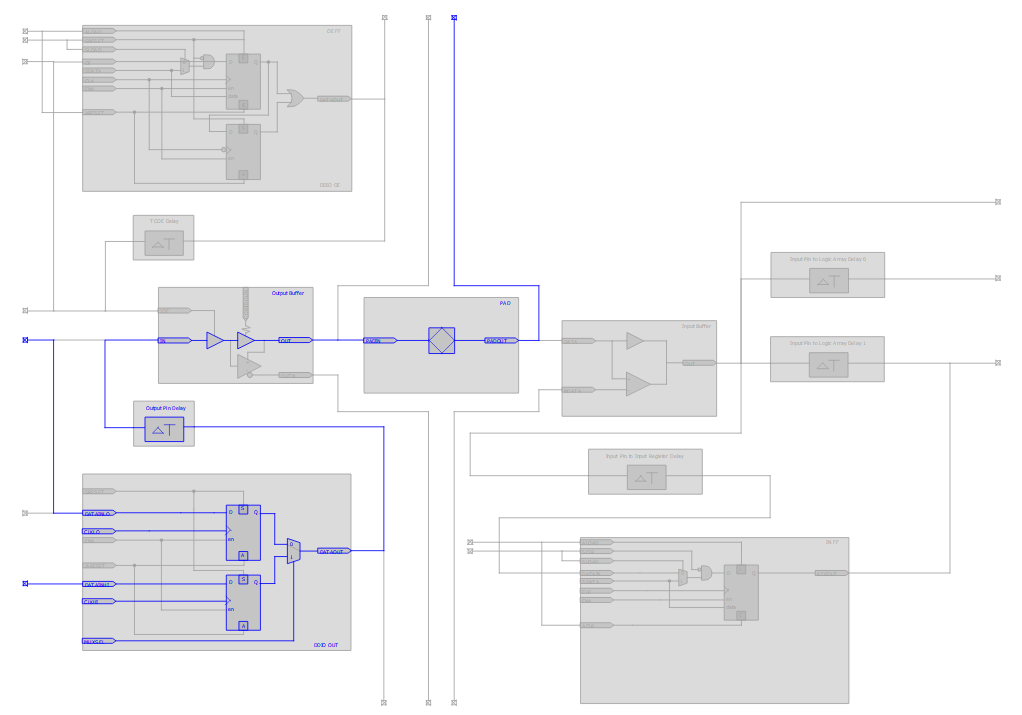

图 3‑20为可编程I/O最小单元内部结构图,包括双向I/O缓冲器、OE寄存器、对齐寄存器、同步寄存器、DDR输出寄存器、三态门、延时模块等。

图 3‑20 可编程I/O最小单元内部结构图

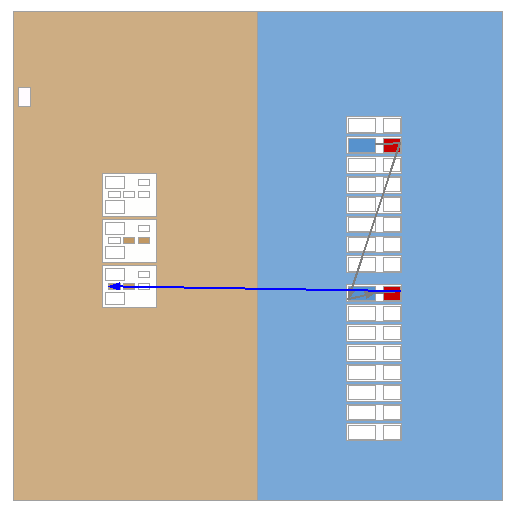

为了便于管理和适应多种电器标准,FPGA 的 IOE 部分被划分为若干个组(Bank),每个 Bank 的接口标准由其接口电压 VCCIO 决定,一个 Bank 只能有一种 VCCIO,但不同 Bank 的 VCCIO 可以不同。只有相同电气标准和物理特性的端口才能连接在一起,VCCIO 电压相同是接口标准的基本条件。图 3‑21为EP4CE10F17C8N芯片“Pin Planner”的整体视图,用于管脚的绑定,图中芯片被划分为8种不同的颜色,每种颜色代表不同的Bank。

图 3‑21 管脚绑定整体视图

互连线资源(Interconnect):布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA 芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同划分为 4 类:第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用于完成芯片 Bank 间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于实现基本逻辑单元之间的逻辑互连;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。图 3‑22中蓝色高亮的连线为由LAB中的LE的寄存器与IOE中的互连线。

图 3‑22 互连线资源

嵌入式存储单元(Memory Bits,也被称为Block RAM或简称为BRAM):该部分资源主要用于生成RAM、ROM、FIFO以及移位寄存器等常用的存储模块,常用于大数据存储或跨时钟域处理,BRAM 由一定数量固定大小的存储块构成的,使用 BRAM 资源不占用额外的逻辑资源,不过使用的时候消耗的 BRAM 资源只能是其块大小的整数倍,就算你只存了 1 bit 也要占用一个 完整的BRAM。

图 3‑23 嵌入式存储单元

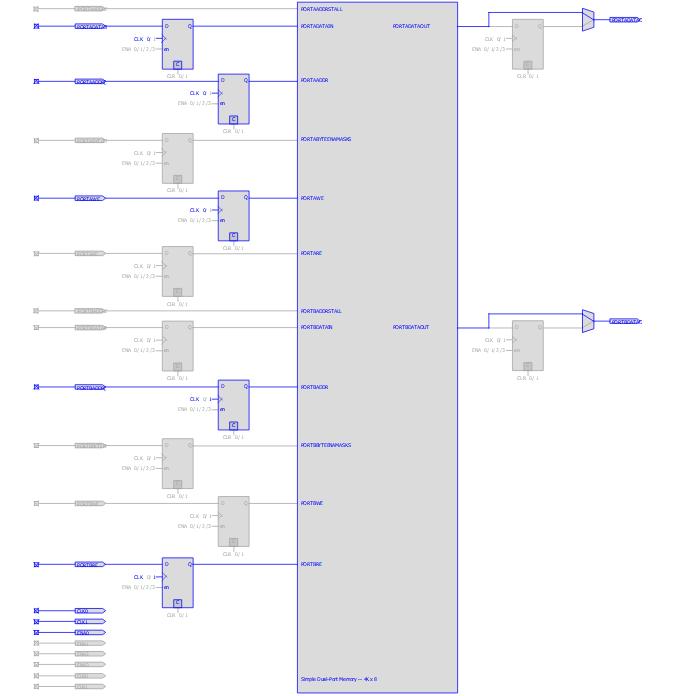

图 3‑24为一个M9K内部结构图。由输入输出寄存器和一个RAM块构成,该芯片共有423936bit存储单元,并以每9Kbit容量为一个块,共有46个,下图所示为一个M9K的RAM块。相对于LUT构成的分布式RAM(Distribute RAM,简称为DRAM),这种专用存储单元速度更快,容量更大,可以避免LUT资源的浪费,只有在 BRAM 资源不够时才不得不使用分布式 RAM。

图 3‑24 M9K内部结构图

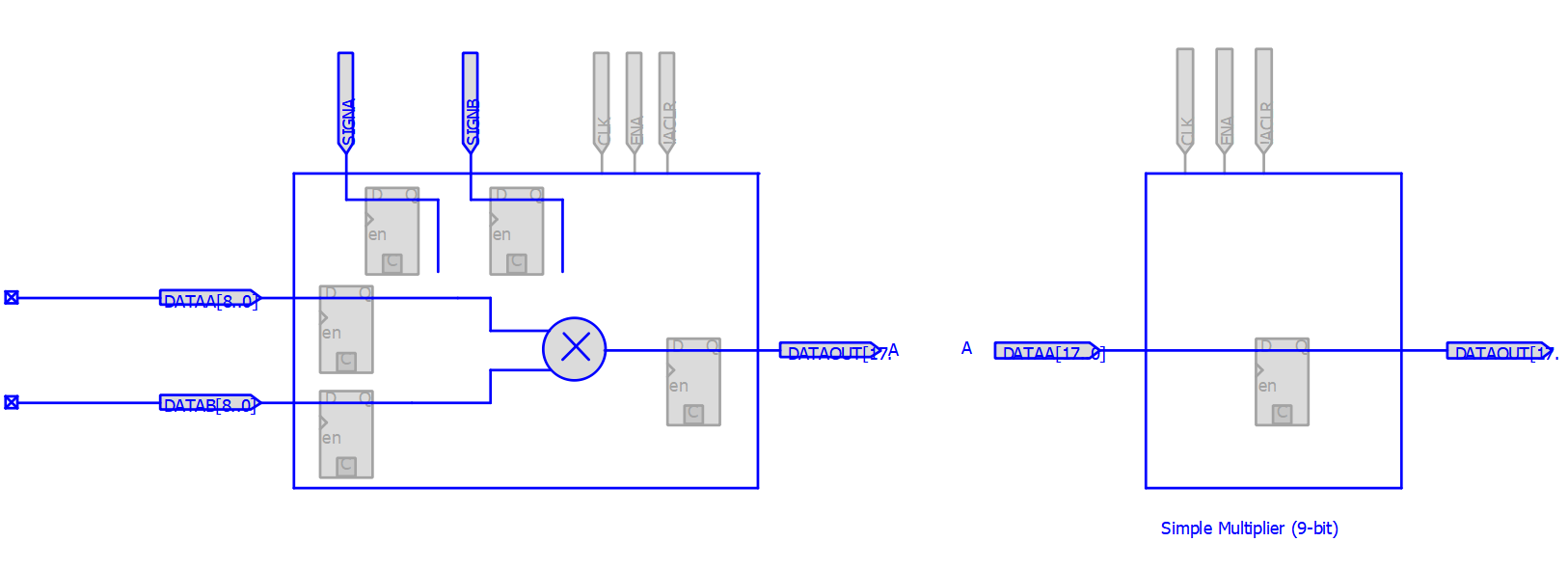

嵌入式乘法单元(Embedded multiPlier 9-bit elements,也简称为DSP块):该单元主要用于各种复杂的数学运算,乘法、除法以及常用的功能函数如:有限冲激响应滤波器(FIR),无限冲击响应滤波器(IIR),快速傅里叶变换(FFT),离散余弦变换(DCT)等,因为FPGA中的 LUT和寄存器资源有限,使用嵌入式乘法单元可大大节省逻辑资源。本芯片共有46个DSP块,成列式分布在芯片的中间位置,图 3‑25为一对DSP块资源。

图 3‑25 一对DSP块资源

图 3‑26为嵌入式乘法器单元DSP块的内部结构;它包含输入输出寄存器和一个乘数块。

图 3‑26 嵌入式乘法器单元DSP块的内部结构图

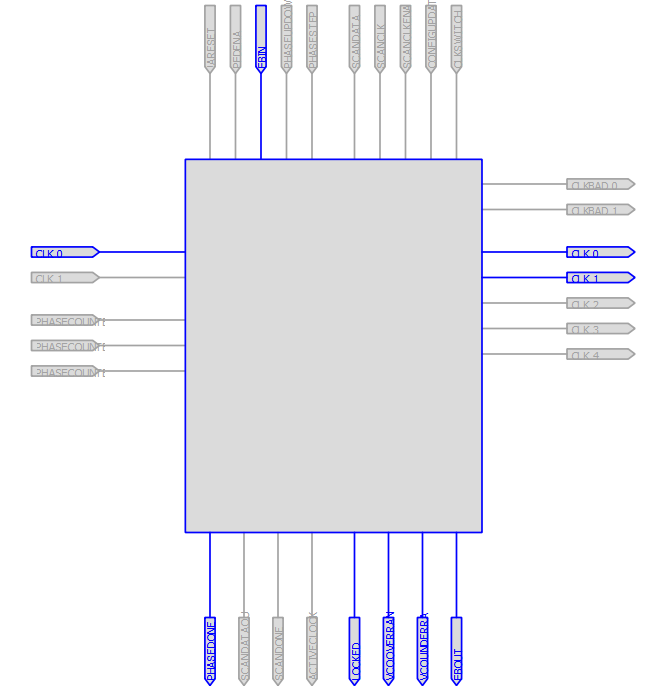

锁相环(Phase Lock Loop,PLL):本芯片一共有两个锁相环,芯片右上角、左下角各一个。PLL的参考时钟由晶振通过专用时钟管脚传入,用于时钟的倍频、分频,以及相位、占空比的调整。PLL输出的时钟信号会连接到全局时钟网络上,以保证时钟的质量,减小时钟偏斜(Skew)和抖动(Jitter)。

图 3‑27 锁相环

图 3‑28为锁相环内部的结构图,每个锁相环可以分出五个同源时钟信号,图中只输出了两路。

图 3‑28 锁相环内部的结构图

不同系列的FPGA芯片其内部资源量会稍有差异,但都会包含以上几类主要的内部资源,上面提到的诸多资源在后面的学习中我们都会使用到,届时再进行详细说明。