4. 简易电压表的设计与验证¶

在上一章节,我们使用外部挂载的高速AD/DA板卡的D/A部分,设计并实现了DDS简易信号发生器。D/A部分是数模转换部分,将输入的数字信号通过DAC芯片转换为模拟信号,A/D部分则相反,实现的是将输入的模拟信号转换为数字信号。我们常用的数字电压表就是使用ADC芯片配合外围电路实现输入模拟信号的电压测 量并显示。

在本章节,我们将会带领读者使用外部挂载的高速AD/DA板卡的A/D部分,设计实现一个简易电压表,并上板验证。

4.1. 理论学习¶

模/数转换器即A/D转换器,或简称ADC(Analog to Digital Conver),通常是指一个将模拟信号转变为数字信号的电子元件或电路。常见的模/数转换器将经过与标准量比较处理后的模拟量转换为以二进制数值表示的离散信号。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易 储存、处理和发射的数字形式。模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。

模拟信号与数字信号的转换过程一般分为四个步骤:采样、保持、量化、编码。前两个步骤在采样-保持电路中完成,后两步则在ADC芯片中完成。

常用的ADC可分为积分型、逐次逼近型、并行比较型/串并行型、Σ -Δ调制型、电容阵列逐次比较型以及压频变换型。

积分型ADC工作原理是将输入电压转换成时间或频率,然后由定时器/计数器获得数字值。其优点是使用简单电路就能获得高分辨率;缺点是由于转换精度依赖于积分时间,因此转换速率极低。双积分是一种常用的AD 转换技术,具有精度高,抗干扰能力强等优点。但高精度的双积分AD芯片,价格昂贵,设计成本较高。

逐次逼近型ADC由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等,优点是速度较高、功耗低,在低分辨率( < 12位)时价格便宜,但高精度( > 12位)价格昂贵。

并行比较型ADC采用多个比较器,仅作一次比较而实行转换,又称Flash型。由于转换速率极高,n位的转换需要2n - 1个比较器,因此电路规模也极大,价格也高,只适用于视频AD 转换器等速度特别高的领域。

Σ- Δ型ADC以很低的采样分辨率( 1位)和很高的采样速率将模拟信号数字化,通过使用过采样、噪声整形和数字滤波等方法增加有效分辨率,然后对ADC输出进行采样抽取处理以降低有效采样速率。Σ-Δ型ADC的电路结构是由非常简单的模拟电路和十分复杂的数字信号处理电路构成。

电容阵列逐次比较型ADC在内置DA转换器中采用电容矩阵方式,也可称为电荷再分配型。一般的电阻阵列DA转换器中多数电阻的值必须一致,在单芯片上生成高精度的电阻并不容易。如果用电容阵列取代电阻阵列,可以用低廉成本制成高精度单片AD转换器。最近的逐次比较型AD转换器大多为电容阵列式的。

压频变换型是通过间接转换方式实现模数转换的。其原理是首先将输入的模拟信号转换成频率,然后用计数器将频率转换成数字量。从理论上讲这种ADC的分辨率几乎可以无限增加,只要采样的时间能够满足输出频率分辨率要求的累积脉冲个数的宽度。其优点是分辨率高、功耗低、价格低,但是需要外部计数电路共同完成AD转换。

ADC的主要技术指标包括:分辨率、转换速率、量化误差、满刻度误差、线性度。

分辨率指输出数字量变化一个最低有效位(LSB)所需的输入模拟电压的变化量。

转换速率是指完成一次从模拟转换到数字的AD转换所需要的时间的倒数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率 。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。

量化误差是由于AD的有限分辩率而引起的误差,即有限分辩率AD的阶梯状转移特性曲线与无限分辩率AD(理想AD)的转移特性曲线(直线)之间的最大偏差。通常是1个或半个最小数字量的模拟变化量,表示为1LSB、1/2LSB。

满刻度误差是满刻度输出时对应的输入信号与理想输入信号值之差。

线性度指实际转换器的转移函数与理想直线的最大偏移。

4.2. 实战演练¶

4.2.1. 实验目标¶

外部挂载的高速AD/DA板卡的A/D部分将输入其中的模拟信号转换为数字量,将数字量传入FPGA,FPGA将传入的数字量通过计数转化为电压数值,通过数码管显示转化后的电压值,实现模拟信号的电压测量。

4.2.2. 硬件资源¶

如图 33‑1所示,我们使用外载AD/DA板卡的AD部分完成本次实验设计;如图 33‑2所示为外载AD/DA板卡AD部分原理图,包括高速AD芯片和外围电路。

图 33‑1 外载AD/DA板卡外观图

图 33‑2 外载AD/DA板卡AD部分原理图

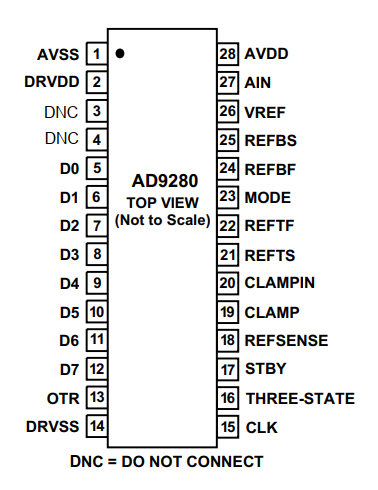

外载AD/DA板卡的AD部分使用高速AD芯片AD9280,AD9280由ANALOG公司生产, 是一款单芯片、8位、32 MSPS模数转换器(ADC),采用单电源供电,内置一个片内采样保持放大器和基准电压源。它采用多级差分流水线架构,数据速率达32 MSPS,在整个工作温度范围内保证无失码。

AD9280的输入经过设计,使成像和通信系统的开发更加轻松。用户可以选择各种输入范围和偏移,并可通过单端或差分方式驱动输入。采样保持放大器(SHA)既适用于在连续通道中切换满量程电平的多路复用系统,也适合采用最高Nyquist速率及更高的频率对单通道输入进行采样。利用片上钳位电路,可以使交流耦合输入 信号偏移到预定电平。动态性能极为出色。

AD9280具有一个片上可编程基准电压源。也可以选用外部基准电压,以满足应用的直流精度与温度漂移要求。采用一个单时钟输入来控制所有内部转换周期。数字输出数据格式为标准二进制。超量程(OTR)信号表示溢出状况,可由最高有效位来确定是下溢还是上溢。

AD9280采用+2.7 V至+5.5 V电源供电,非常适合高速应用中的低功耗操作,额定温度范围为-40°C至+85°C工业温度范围。引脚图及内部结构图如下图 33‑3、图 33‑4所示。关于AD9708的更多详细资料可查阅数据手册。

图 33‑3 AD9280引脚图

图 33‑4 AD9280内部结构图

4.3. 程序设计¶

4.3.1. 整体说明¶

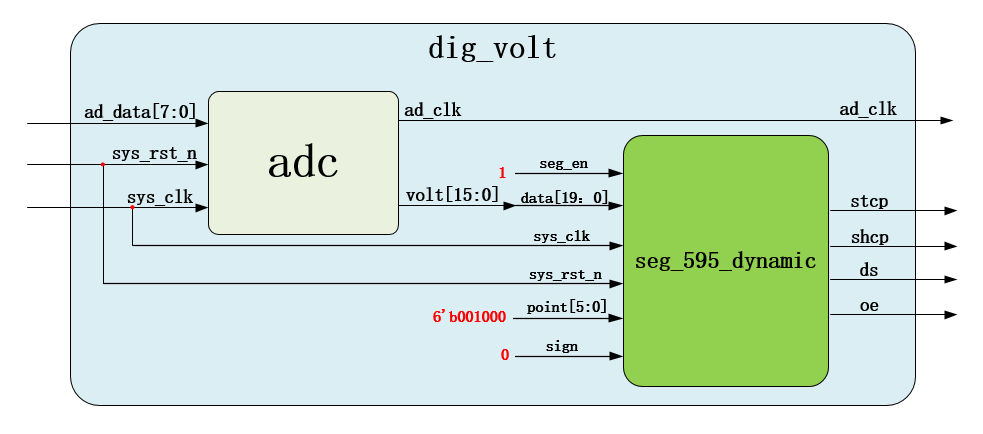

实验工程整体框图,具体见图 33‑5。

图 33‑5 实验工程整体框图

将待测量的模拟信号接入外部挂载的高速AD/DA板卡的模拟信号输入端,板卡会将输入的模拟信号进行采样、量化、编码后,将模拟电压转换为数字值传给FPGA;内部adc模块接收到传入的电压数字值,经过运算,转换为可用于显示的电压值输入给数码管显示模块,将电压值显示在数码管上。

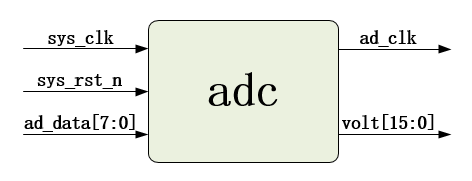

4.3.1.1. ADC模块¶

模块框图

图 33‑6 ADC模块框图

由ADC模块框图可知,模块有3路输入信号和2路输出信号。输入信号有时钟、复位和外载板卡传入的模拟信号电压数字值ad_data;输出信号有2路,ad_clk信号为传入外载板卡的时钟信号,频率为12.5MH中,由系统时钟信号4分频得到,ADC芯片在此时钟同步下进行模拟信号的采样、量化和编码,volt信号 则是经过运算处理后的电压值,传入数码管显示模块用于电压显示。

波形图绘制

本实验使用的ADC芯片位宽为8位,板卡模拟电压输入范围为-5v~+5v,即电压表测量范围,最大值和最小值压降为10v,分辨率为10/28。

当ADC芯片采集后的电压数值ad_data位于0 - 127范围内,表示测量电压位于-5V ~ 0V范围内,换算为电压值:Vin = - (10 / 28 * (127 - ad_data));当ADC芯片采集后的电压数值ad_data位于128 - 255范围内,表示测量电压位于0V ~ 5V范围内,换算为电压值:Vin = (10 / 28 * (ad_data - 127))。

简易电压表实验可以参照这种思想来进行工程的设计与实现,但为了提高测量结果的精确性,我们使用定义中值的测量方法。

在电压表上电后未接入测量电压时,取ADC芯片采集的最初的若干测量值,取平均,作为测量中值data_median,与实际测量值0V对应。

使用定义中值的测量方法时,当ADC芯片采集后的电压数值ad_data位于0 - data_median范围内,表示测量电压位于-5V ~ 0V范围内,分辨率为10/((data_median + 1) * 2),换算为电压值:Vin = - ((10 /((data_median + 1) * 2)) * (data_median - ad_data));当ADC芯片采集后的电压数值ad_data位于data_median - 255范围内,表示测量电压位于0V ~ 5V范围内,分辨率为10/((255 - data_median + 1) * 2),换算为电压值:Vin = ((10 /((255 - data_median + 1) * 2)) * (ad_data - data_median))。

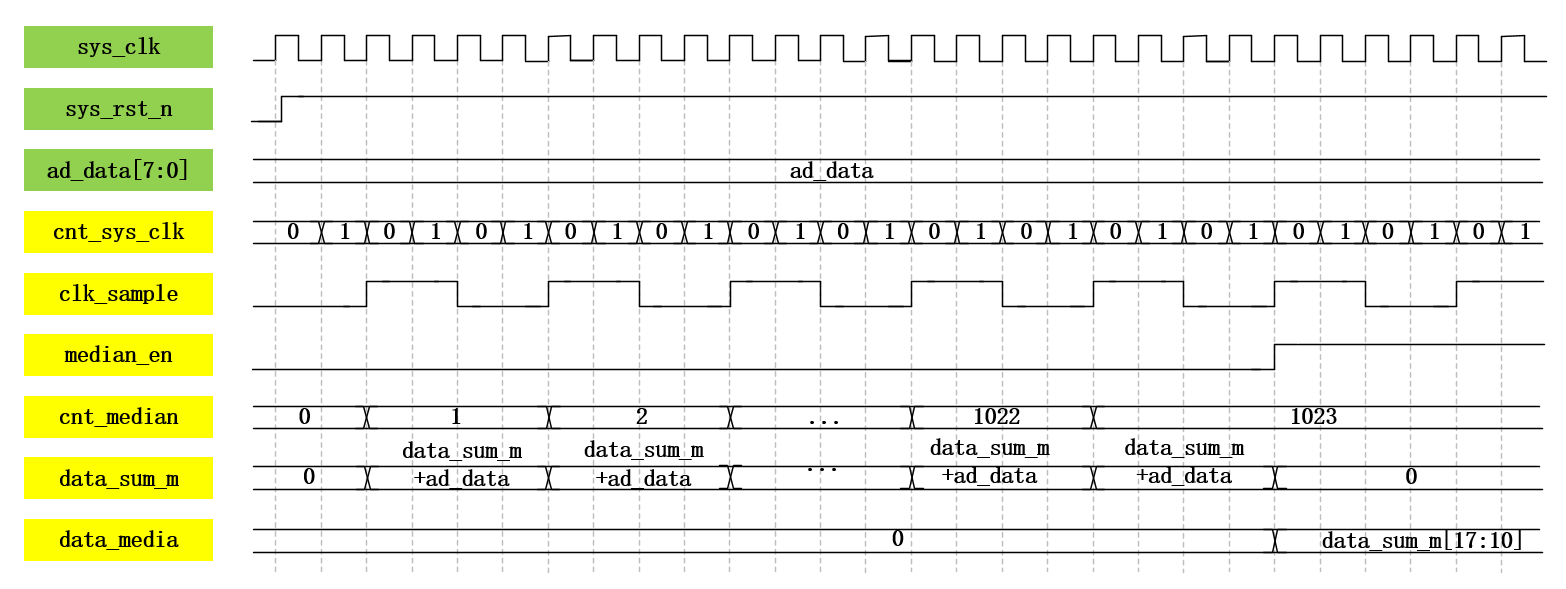

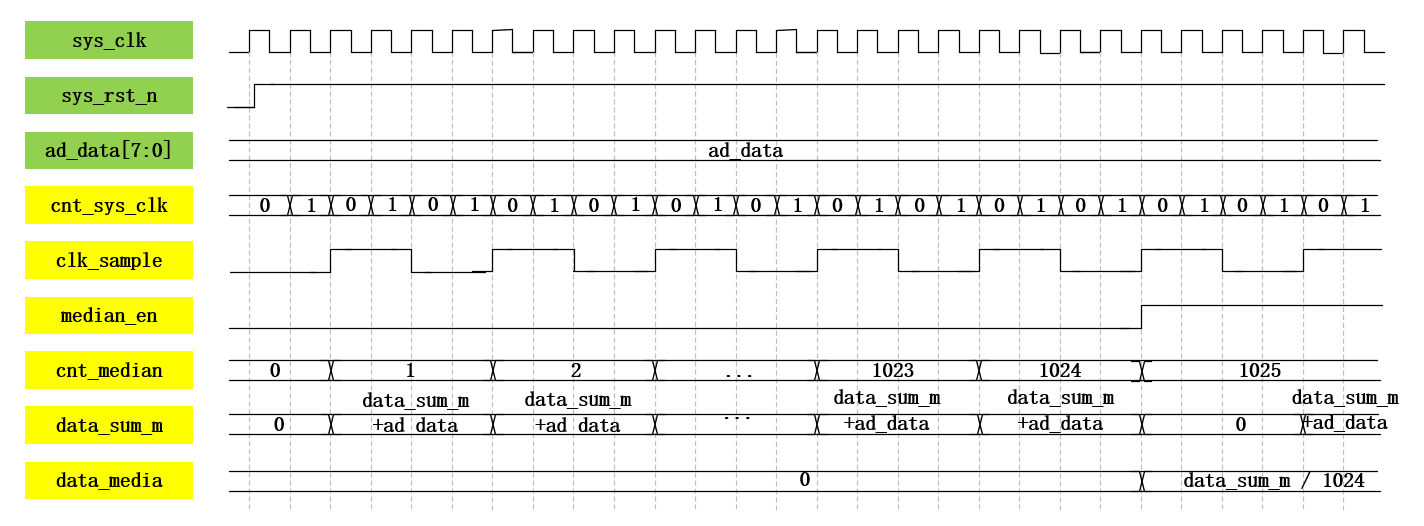

了解了具体的实现方法,我们开始波形图绘制。模块波形图,具体见图 33‑7、图 33‑8。

图 33‑7 ADC模块波形图(一)

图 33‑8 ADC模块波形图(二)

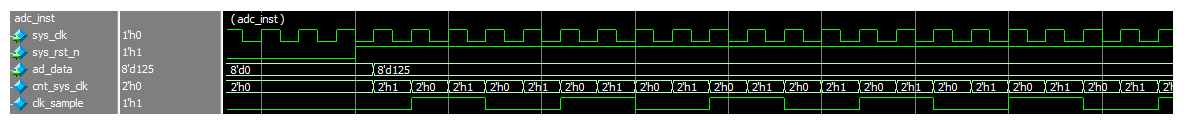

对于模块的输入信号不再说明,输出至外载板块的的时钟信号为ad_clk,频率为12.5MHz,使用系统时钟4分频得来,所以声明了分频计数器cnt_sys_clk,初值为0,在系统时钟同步下,在0、1之间循环计数;声明时钟信号clk_sample,在计数器cnt_sys_clk计数值为1时,对自身取反, 就得到了时钟频率为12.5MHz的分频时钟信号clk_sample,也作为本模块工作时钟信号;因为外载板卡与本模块均使用时钟上升沿对数据采样,为保证模块内工作时钟上升沿能够采集到板块传入的稳定数据,我们对clk_sample时钟信号取反作为输入板卡的时钟信号adc_clk,adc_clk的上升沿刚好 采集到数据的稳定状态。

声明中值使能信号median_en,方便计算中值,当median_en信号为低电平时,进行中值的计算;当median_en信号为高电平时,对ADC测量值进行累加求平均的计算。

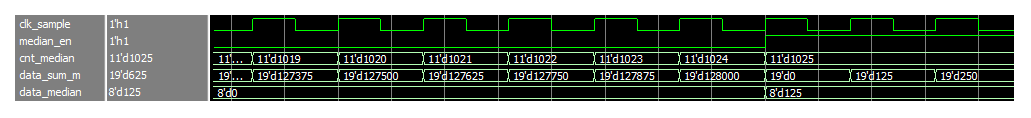

对中值的计算我们也使用累加求平均的方法,在无测量电压输入电压表时,对前1024个数据进行累加求平均,所以声明计数器cnt_median对累加值个数进行计数,计算范围0-1023,只在median_en为低电平时进行计数,median_en为高电平时,保持计数最大值;同时,计数最大值作为条件,拉高me dian_en使能信号。1024个测量值总和保存在变量data_sum_m中,当cnt_median计数到最大值,将平均值赋值给变量data_median。

中值data_median确定后,开始测量电压的计算。当ADC芯片采集后的电压数值ad_data位于0 - data_median范围内,表示测量电压位于-5V ~ 0V范围内,分辨率为10/((data_median + 1) * 2),换算为电压值:Vin = - ((10 /((data_median + 1) * 2)) * (data_median -

ad_data));当ADC芯片采集后的电压数值ad_data位于data_median - 255范围内,表示测量电压位于0V ~ 5V范围内,分辨率为10/((255 - data_median + 1) * 2),换算为电压值:Vin = ((10 /((255 - data_median + 1) * 2)) * (ad_data - data_median))。

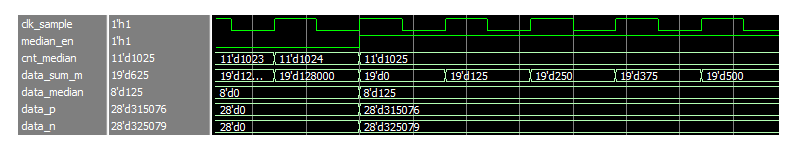

为保证运算后的电压值更准确,我们对计算出的分辨率进行放大。当ADC芯片采集后的电压数值ad_data位于0 - data_median范围内,表示测量电压位于-5V ~ 0V范围内,声明分辨率为data_n = (10 * 2^13 * 1000) / ((data_median + 1) * 2);当ADC芯片采集后的电压数值ad_data位于data_median -

255范围内,表示测量电压位于0V ~ 5V范围内,声明分辨率为data_p = (10 * 2^13 * 1000) / ((255 - data_median + 1) * 2)。放大倍数为(2^13 * 1000)倍,之所以使用这个放大倍数是为了方便电压值的计算与显示。

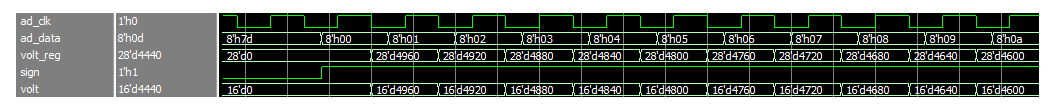

确定了分辨率之后,结合ADC芯片传入的测量值,我们开始计算实际电压值。声明实际电压值为volt_reg,当ADC芯片采集后的电压数值ad_data位于0 - data_median范围内,表示测量电压位于-5V ~ 0V范围内,volt_reg = (data_n *(data_median - ad_data)) >> 13;当ADC芯片采集后的电压数值ad_data位于data_median - 255范围内,表示测量电压位于0V ~

5V范围内,volt_reg = (data_p *(ad_data

data_median)) >> 13。使用 “>> 13”对计算值进行右移13位,由于抵消分辨率放大的2^13倍,分辨率中放大的1000倍,可以通过将数码管显示值小数点左移3位来抵消;正负号通过ad_data与中值data_median的打消比较来确定,sign = (ad_data < data_median) ? 1’b1 : 1’b0,sign为高电平,代表测量结果为负向电压,反之为正向电压。

代码编写

参照波形图编写参考代码,具体见代码清单 33‑1。

代码清单 33‑1 ADC模块参考代码(adc.v)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 | module adc

(

input wire sys_clk , //时钟

input wire sys_rst_n , //复位信号,低电平有效

input wire [7:0] ad_data , //AD输入数据

output wire ad_clk , //AD驱动时钟,最大支持20MHz时钟

output wire sign , //正负符号位

output wire [15:0] volt //数据转换后的电压值

);

////

//Parameter And Internal Signal \//

////

//parameter define

parameter CNT_DATA_MAX = 11'd1024; //数据累加次数

//wire define

wire [27:0] data_p ; //根据中值计算出的正向电压AD分辨率

wire [27:0] data_n ; //根据中值计算出的负向电压AD分辨率

//reg define

reg median_en ; //中值使能

reg [10:0] cnt_median ; //中值数据累加计数器

reg [18:0] data_sum_m ; //1024次中值数据累加总和

reg [7:0] data_median ; //中值数据

reg [1:0] cnt_sys_clk ; //时钟分频计数器

reg clk_sample ; //采样数据时钟

reg [27:0] volt_reg ; //电压值寄存

////

//\* Main Code \//

////

//数据ad_data是在ad_sys_clk的上升沿更新

//所以在ad_sys_clk的下降沿采集数据是数据稳定的时刻

//FPGA内部一般使用上升沿锁存数据,所以时钟取反

//这样ad_sys_clk的下降沿相当于sample_sys_clk的上升沿

assign ad_clk = ~clk_sample;

//sign:正负符号位

assign sign = (ad_data < data_median) ? 1'b1 : 1'b0;

//时钟分频(4分频,时钟频率为12.5MHz),产生采样AD数据时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

begin

cnt_sys_clk <= 2'd0;

clk_sample <= 1'b0;

end

else

begin

cnt_sys_clk <= cnt_sys_clk + 2'd1;

if(cnt_sys_clk == 2'd1)

begin

cnt_sys_clk <= 2'd0;

clk_sample <= ~clk_sample;

end

end

//中值使能信号

always@(posedge clk_sample or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

median_en <= 1'b0;

else if(cnt_median == CNT_DATA_MAX)

median_en <= 1'b1;

else

median_en <= median_en;

//cnt_median:中值数据累加计数器

always@(posedge clk_sample or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_median <= 11'd0;

else if(median_en == 1'b0)

cnt_median <= cnt_median + 1'b1;

//data_sum_m:1024次中值数据累加总和

always@(posedge clk_sample or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

data_sum_m <= 19'd0;

else if(cnt_median == CNT_DATA_MAX)

data_sum_m <= 19'd0;

else

data_sum_m <= data_sum_m + ad_data;

//data_median:中值数据

always@(posedge clk_sample or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

data_median <= 8'd0;

else if(cnt_median == CNT_DATA_MAX)

data_median <= data_sum_m / CNT_DATA_MAX;

else

data_median <= data_median;

//data_p:根据中值计算出的正向电压AD分辨率(放大2^13*1000倍)

//data_n:根据中值计算出的负向电压AD分辨率(放大2^13*1000倍)

assign data_p=(median_en==1'b1)?8192_0000/((255-data_median)*2):0;

assign data_n=(median_en==1'b1)?8192_0000/((data_median+1)*2):0;

//volt_reg:处理后的稳定数据

always@(posedge clk_sample or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

volt_reg <= 'd0;

else if(median_en == 1'b1)

if((ad_data > (data_median - 3))&&(ad_data < (data_median + 3)))

volt_reg <= 'd0;

else if(ad_data < data_median)

volt_reg <= (data_n \*(data_median - ad_data)) >> 13;

else if(ad_data > data_median)

volt_reg <= (data_p \*(ad_data - data_median)) >> 13;

else

volt_reg <= 'd0;

//volt:数据转换后的电压值

assign volt = volt_reg;

endmodule

|

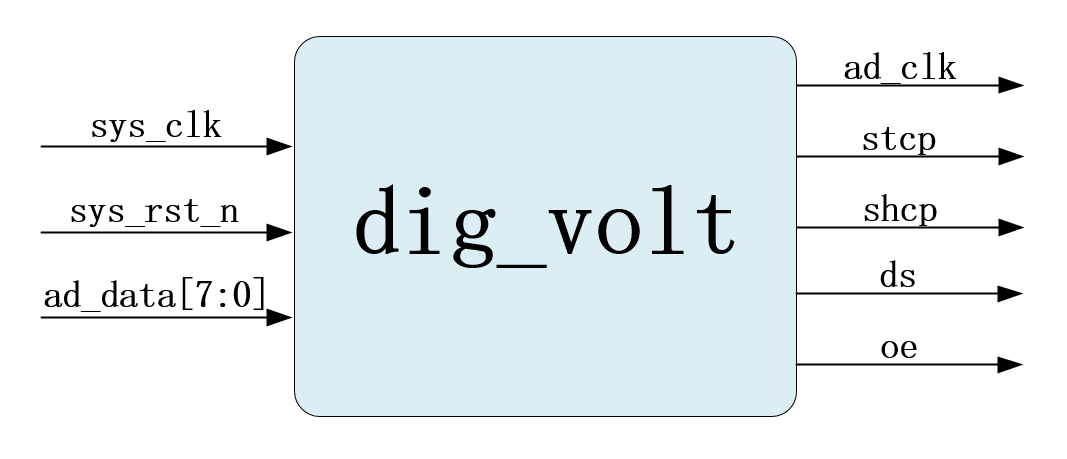

4.3.1.2. 顶层模块¶

模块框图

顶层模块较为简单,内部例化了各子功能模块,连接各对应信号;外部有3路输入信号、3路输出信号。输入有时钟、复位信号和办卡采集的8位二进制模拟信号数据;输出3路信号中,时钟信号ad_clk为输入外载板卡,作为板卡工作时钟;信号stcp、shcp、ds、oe用于驱动数码管显示。

顶层模块框图,具体见图 33‑9。

图 33‑9 顶层模块框图

代码编写

顶层模块无需波形图的绘制,字节编写参考代码,具体见代码清单 33‑2。

代码清单 33‑2 顶层模块参考代码(dig_volt.v)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 | module dig_volt

(

input wire sys_clk , //系统时钟,50MHz

input wire sys_rst_n , //复位信号,低有效

input wire [7:0] ad_data , //AD输入数据

output wire ad_clk , //AD驱动时钟,最大支持20MHz时钟

output wire stcp , //数据存储器时钟

output wire shcp , //移位寄存器时钟

output wire ds , //串行数据输入

output wire oe //使能信号

);

////

//Internal Signal \//

////

//wire define

wire [15:0] volt ; //数据转换后的电压值

wire sign ; //正负符号位

////

//\* Instantiation \//

////

//------------- adc_inst -------------

adc adc_inst

(

.sys_clk (sys_clk ), //时钟

.sys_rst_n (sys_rst_n ), //复位信号,低电平有效

.ad_data (ad_data ), //AD输入数据

.ad_clk (ad_clk ), //AD驱动时钟,最大支持20MHz时钟

.sign (sign ), //正负符号位

.volt (volt ) //数据转换后的电压值

);

//------------- seg_595_dynamic_inst --------------

seg_595_dynamic seg_595_dynamic_inst

(

.sys_clk (sys_clk ), //系统时钟,频率50MHz

.sys_rst_n (sys_rst_n ), //复位信号,低有效

.data (volt ), //数码管要显示的值

.point (6'b001000 ), //小数点显示,高电平有效

.seg_en (1'b1 ), //数码管使能信号,高电平有效

.sign (sign ), //符号位,高电平显示负号

.stcp (stcp ), //输出数据存储寄时钟

.shcp (shcp ), //移位寄存器的时钟输入

.ds (ds ), //串行数据输入

.oe (oe ) //输出使能信号

);

endmodule

|

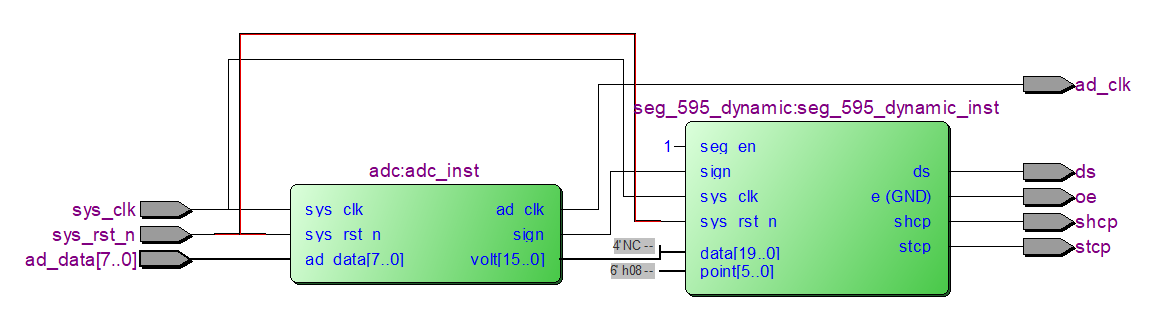

4.3.1.3. RTL视图¶

顶层模块介绍完毕,使用Quartus II软件对实验工程进行编译,工程通过编译后查看实验工程RTL视图。工程RTL视图,具体见图 33‑10。由图可知,实验工程的RTL视图与实验整体框图相同,各信号线均已正确连接。

图 33‑10 RTL视图

4.3.1.4. 仿真验证¶

仿真代码编写

对顶层模块进行仿真验证,仿真参考代码,具体见代码清单 33‑3。

代码清单 33‑3 顶层模块仿真参考代码(tb_dig_volt.v)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 | module tb_dig_volt();

//wire define

wire ad_clk ;

wire shcp ;

wire stcp ;

wire ds ;

wire oe ;

//reg define

reg sys_clk ;

reg sys_rst_n ;

reg data_en ;

reg [7:0] ad_data_reg ;

reg [7:0] ad_data ;

//sys_rst_n,sys_clk,ad_data

initial

begin

sys_rst_n = 1'b0;

sys_clk = 1'b0;

#200;

sys_rst_n = 1'b1;

data_en = 1'b0;

#499990;

data_en = 1'b1;

end

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

ad_data_reg <= 8'd0;

else if(data_en == 1'b1)

ad_data_reg <= ad_data_reg + 1'b1;

else

ad_data_reg <= 8'd0;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

ad_data <= 8'd0;

else if(data_en == 1'b0)

ad_data <= 8'd125;

else if(data_en == 1'b1)

ad_data <= ad_data_reg;

else

ad_data <= ad_data;

always #10 sys_clk = ~sys_clk;

//------------- dig_volt_inst -------------

dig_volt dig_volt_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.ad_data (ad_data ),

.ad_clk (ad_clk ),

.shcp (shcp ),

.stcp (stcp ),

.ds (ds ),

.oe (oe )

);

endmodule

|

仿真波形分析

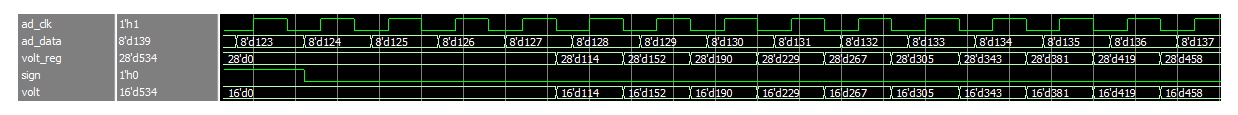

ADC模块仿真波形图如下。模块仿真波形图与绘制波形图各信号波形吻合,模块通过仿真验证。

图 33‑11 ADC模块局部仿真波形图(一)

由图可知,系统时钟sys_clk通过四分频正确生成模块所需时钟信号clk_sample。

图 33‑12 ADC模块局部仿真波形图(二)

图 33‑13 ADC模块局部仿真波形图(三)

由上面两图可知,对无测量电压输入时的前1024次数据进行累加求平均,正确得到中值data_median。

图 33‑14 ADC模块局部仿真波形图(四)

使用计算出的中值data_median,求得正负电压方向的分辨率。

图 33‑15 ADC模块局部仿真波形图(五)

图 33‑16 ADC模块局部仿真波形图(六)

利用公式对ADC芯片采集的测量值进行计算,得出可用于显示的实际电压值。

4.4. 上板验证¶

4.4.1. 引脚约束¶

仿真验证通过后,准备上板验证,上板验证之前先要进行引脚约束。工程中各输入输出信号与开发板引脚对应关系如表格 33‑1所示。

表格 33‑1 引脚分配表

信号名 |

信号类型 |

对应引脚 |

备注 |

|---|---|---|---|

sys_clk |

Input |

E1 |

输入系统时钟 |

sys_rst_n |

Input |

M15 |

复位信号 |

ad_clk |

Output |

A13 |

输出至ADC_CLK |

ad_data[7] |

Input |

A12 |

输入测量值ADC_D7 |

ad_data [6] |

Input |

B12 |

输入测量值ADC_D6 |

ad_data [5] |

Input |

A11 |

输入测量值ADC_D5 |

ad_data [4] |

Input |

B11 |

输入测量值ADC_D4 |

ad_data [3] |

Input |

A15 |

输入测量值ADC_D3 |

ad_data [2] |

Input |

F9 |

输入测量值ADC_D2 |

ad_data [1] |

Input |

F11 |

输入测量值ADC_D1 |

ad_data [0] |

Input |

B9 |

输入测量值ADC_D0 |

stcp |

Output |

B1 |

存储寄存器时钟 |

shcp |

Output |

K9 |

移位寄存器时钟 |

ds |

Output |

R1 |

串行数据 |

oe |

Output |

L11 |

输出使能,低有效 |

下面进行管脚分配,管脚的分配方法在前面章节已有所讲解,在此就不再过多叙述,管脚的分配如下图 33‑17所示。

图 33‑17 管脚分配

4.4.1.1. 结果验证¶

如图 33‑18所示,开发板连接12V直流电源和USB-Blaster下载器JTAG端口。线路正确连接后,打开开关为板卡上电;连接外载AD/DA板卡与开发板底板,连接SMA信号线。

图 33‑18 程序下载连线图

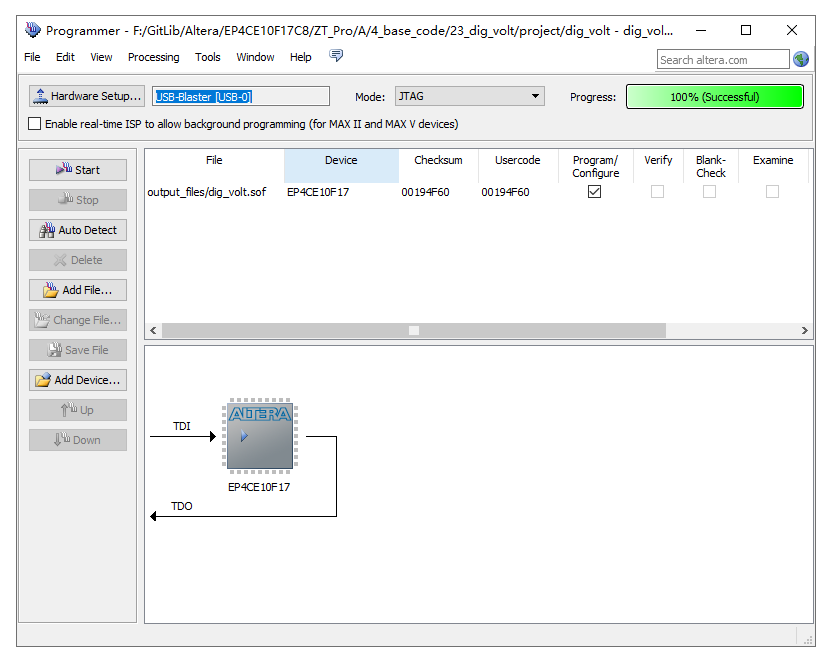

如图 33‑19所示,使用“Programmer”为开发板下载程序。

图 33‑19 程序下载窗口

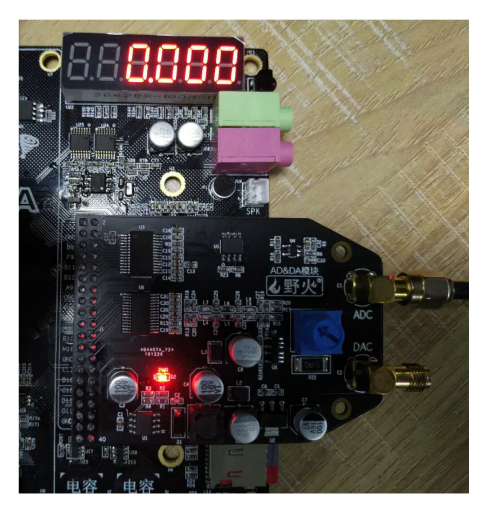

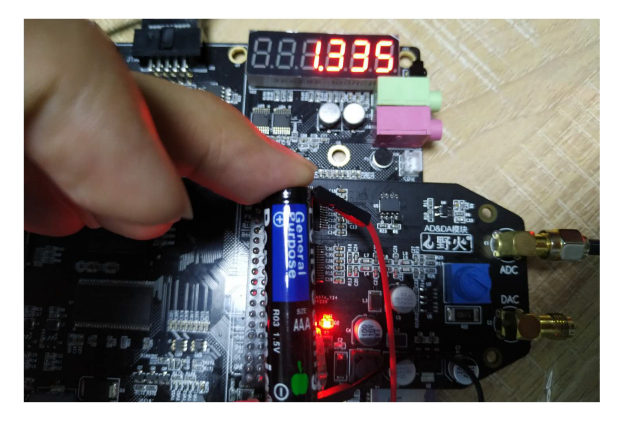

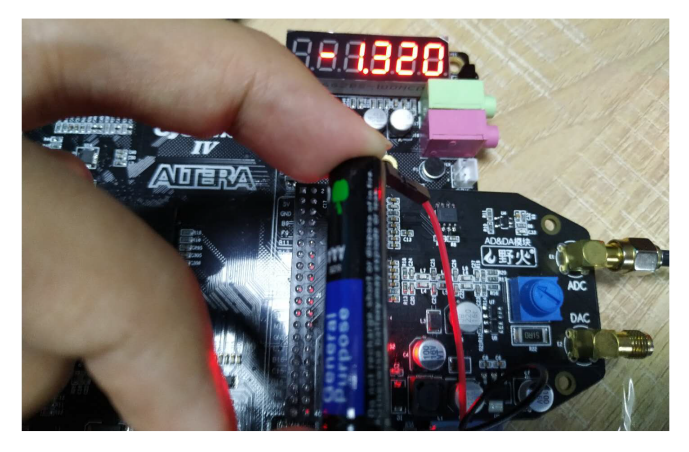

程序下载完成后,开始对简易电压表进行测试验证,如图 33‑20、图 33‑21、图 33‑22、图 33‑23所示。

图 33‑20 上板验证(一)

程序下载完成后,当无测试电压输入简易电压表时,数码管显示测试结果为0.000V。

图 33‑21 上板验证(二)

图 33‑22 上板验证(三)

使用简易电压表对一节使用过的7号干电池进行电压测量:正向电压测量结果为1.335V;反向电压测量结果为-1.320V。

图 33‑23 上板验证(四)

使用专业电压表对干电池进行电压测量,测量电压为1.338V,本实验设计的简易电压表测量结果与专业电压表测量结果误差在可接受范围内,简易电压表验证通过。

4.5. 章末总结¶

在本章节中,我们实现了简易电压表的设计与验证,并通过对这一实验工程的讲解,为读者介绍了ADC的相关知识,希望读者认真学习、切实掌握相关知识。

4.6. 拓展训练¶

在本章节的实验中,我们使用的时定义中值的测量方法,读者在掌握这种方法后可尝试是由其他算法设计实现简易电压表。