8. 避免Latch的产生¶

8.1. 章节导读¶

本章主要讲解Latch是什么,以及它的产生、危害、如何避免等相关知识,目的是为了让大家在设计相关的电路时能够更加规范,从而避免出现不可预测的问题。

8.2. Latch是什么¶

Latch其实就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息。锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,则数据被锁存,输入信号不起作用。因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的。

8.3. Latch的危害¶

之所以在这里讲关于Latch的问题是因为只有组合逻辑才会产生这种问题,产生Latch是我们在同步电路中尽量避免的,但并不表示Latch没有用的或者说是错误的,Latch在异步电路中是非常有用的,只是我们设计的是同步电路,要尽量避免。

在同步电路中Latch会产生不好的效果,如对毛刺敏感;不能异步复位,上电后处于不定态;还会让静态时序分析变得十分复杂;在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用使用寄存器来组成锁存器所以会占用更多逻辑资源;在ASIC设计中,锁存器也会带来额外的延时和DFT,并不利于提高系统的工作频 率,所以要避免产生。在这里我们把会产生组合逻辑的几种情况列举出来,希望大家以后能够避免出现类似的问题。

8.4. 几种产生Latch的情况¶

关于Latch的介绍如果能够理解原理最好,如对原理理解不透彻可以先记住规范的写法,避免产生不可控的因素,从而综合出更好的电路。以下不规范的3种产生Latch的写法一定要尽量避免。

组合逻辑中if语句没有else;

组合逻辑中case的条件不能够完全列举时且不写default;

组合逻辑中输出变量赋值给自己。

情况一:组合逻辑中if语句没有else

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 | module latch_one

(

input wire in1 , //输入信号in1

input wire in2 , //输入信号in2

input wire in3 , //输入信号in3

output reg [7:0] out //输出信号out

);

//out:根据3个输入信号选择输出对应的8bit out信号

always@(*)

if({in1, in2, in3} == 3'b000)

out = 8'b0000_0001;

else if({in1, in2, in3} == 3'b001)

out = 8'b0000_0010;

else if({in1, in2, in3} == 3'b010)

out = 8'b0000_0100;

else if({in1, in2, in3} == 3'b011)

out = 8'b0000_1000;

else if({in1, in2, in3} == 3'b100)

out = 8'b0001_0000;

else if({in1, in2, in3} == 3'b101)

out = 8'b0010_0000;

else if({in1, in2, in3} == 3'b110)

out = 8'b0100_0000;

else if({in1, in2, in3} == 3'b111)

out = 8'b1000_0000;

// else 把最后一个if的else注释掉

// out = 8'b0000_0001;

endmodule

|

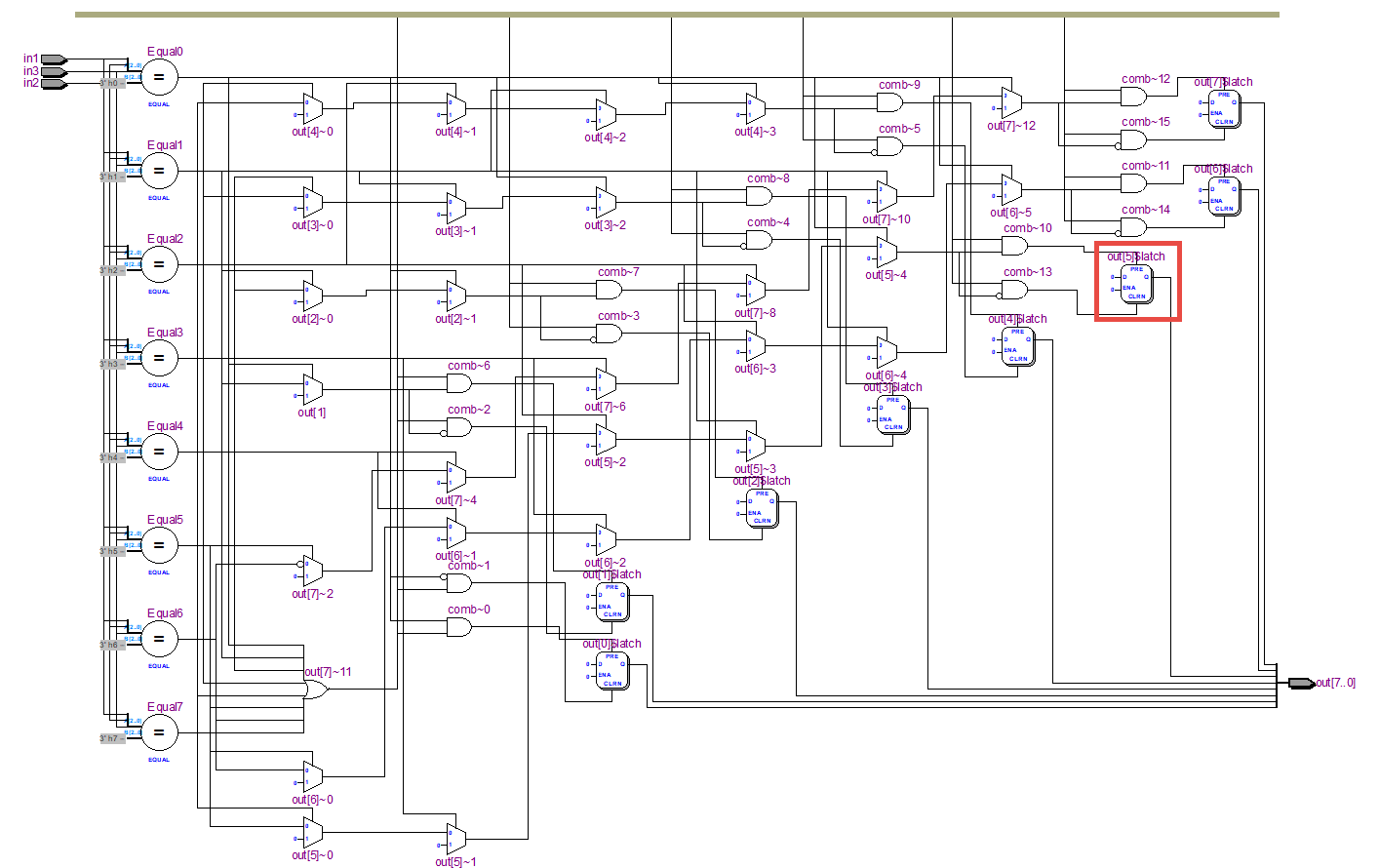

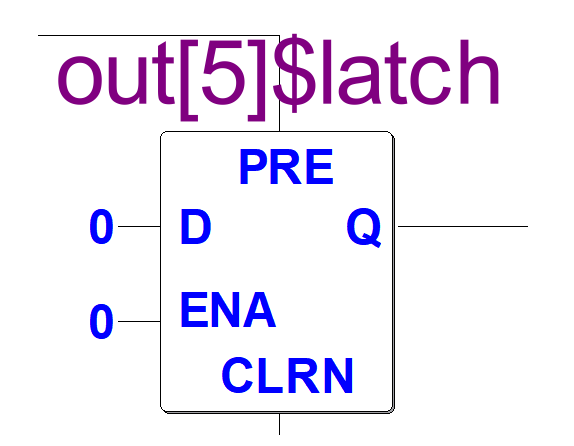

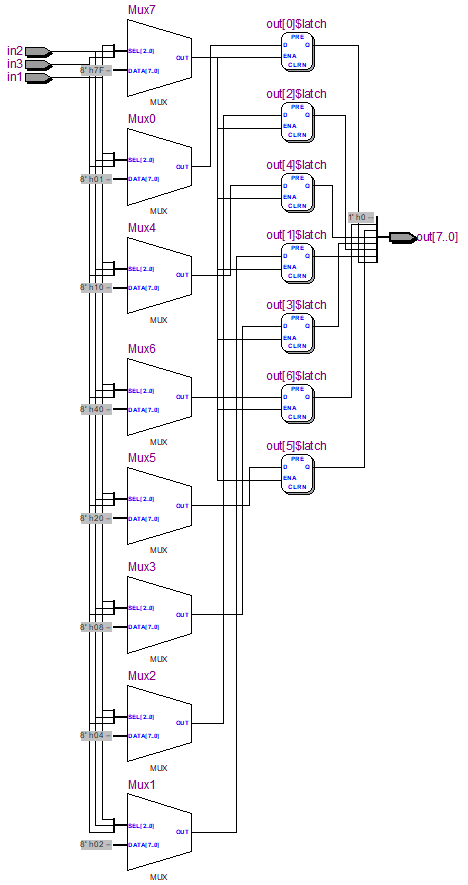

根据上面RTL代码综合出的RTL视图如图 14‑1所示,我们可以看到其结构相当的复杂,红色中的结构即为Latch锁存器,如图 14‑2所示。

图 14‑1 RTL视图(一)

图 14‑2 Latch锁存器

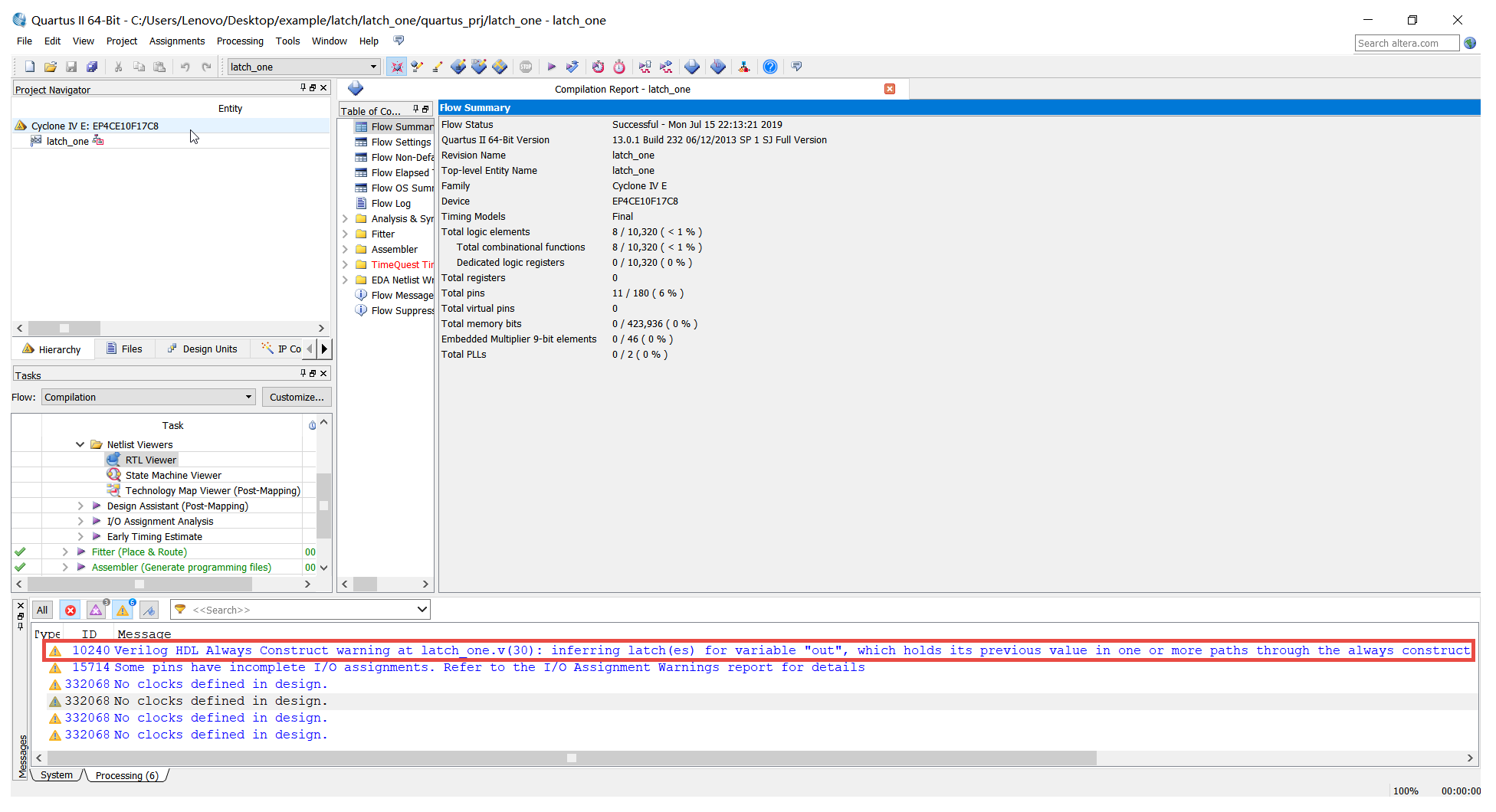

在综合后的界面的“Messages”窗口中提示输出有“latch”产生,此时我就应该关注一下此“latch”是否真的是我们有意产生的。

图 14‑3 Messages窗口提示

情况二:组合逻辑中case的条件不能够完全列举且不写default

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 | module latch_two

(

input wire in1 , //输入信号in1

input wire in2 , //输入信号in2

input wire in3 , //输入信号in2

output reg [7:0] out //输出信号out

);

//out:根据3个输入信号选择输出对应的8bit out信号

always@(*)

case({in1, in2, in3})

3'b000 : out = 8'b0000_0001;

3'b001 : out = 8'b0000_0010;

3'b010 : out = 8'b0000_0100;

3'b011 : out = 8'b0000_1000;

3'b100 : out = 8'b0001_0000;

3'b101 : out = 8'b0010_0000;

3'b110 : out = 8'b0100_0000;

//把最后一种情况和default都注释掉,使case的条件不能够完全列举

//3'b111 : out = 8'b1000_0000;

//default: out = 8'b0000_0001;

endcase

endmodule

|

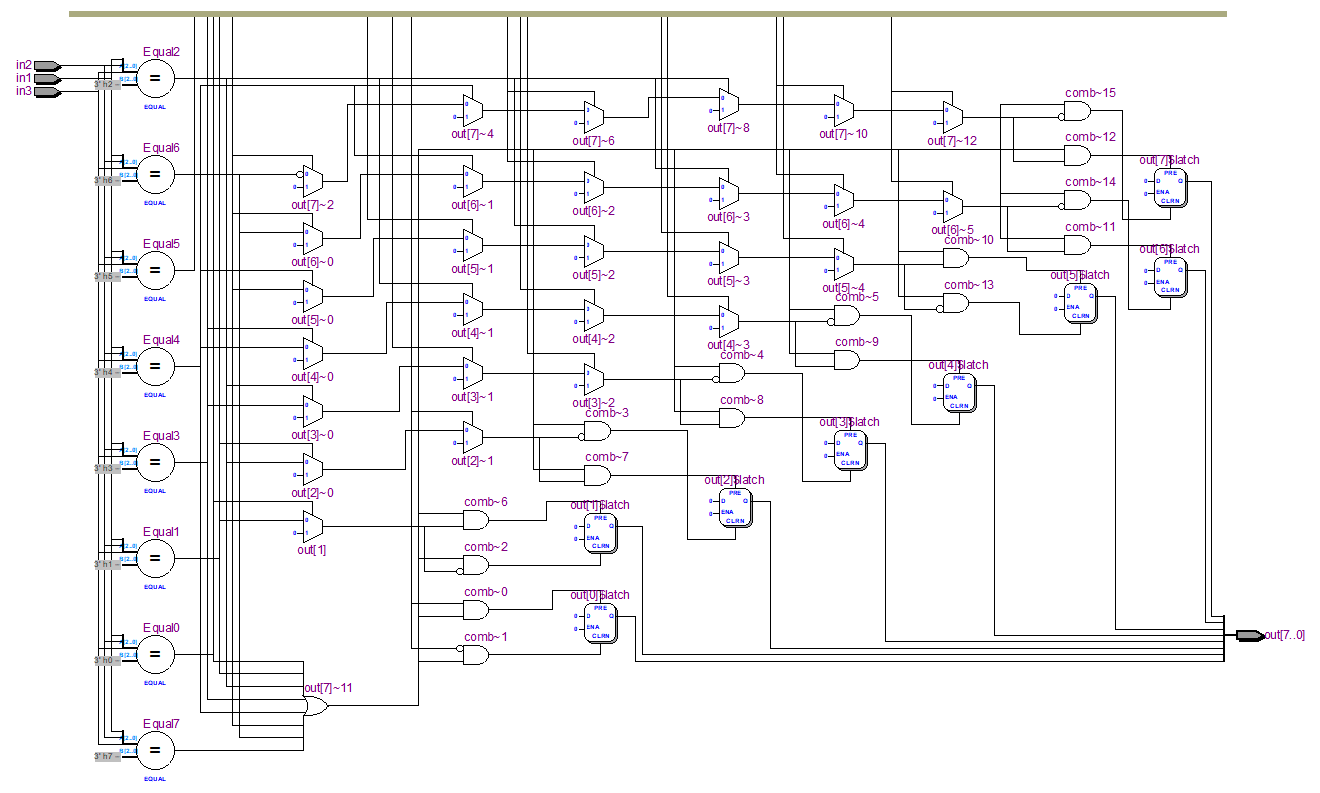

根据上面RTL代码综合出的RTL视图如图 14‑4所示,我们可以看到也产生了latch。

图 14‑4 RTL视图(二)

情况三:组合逻辑中输出变量赋值给自己(一)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 | module latch_three

(

input wire in1 , //输入信号in1

input wire in2 , //输入信号in2

input wire in3 , //输入信号in3

output reg [7:0] out //输出信号out

);

//out:根据3个输入信号选择输出对应的8bit out信号

always@(*)

if({in1, in2, in3} == 3'b000)

out = 8'b0000_0001;

else if({in1, in2, in3} == 3'b001)

out = 8'b0000_0010;

elseif({in1, in2, in3} == 3'b010)

out = 8'b0000_0100;

elseif({in1, in2, in3} == 3'b011)

out = 8'b0000_1000;

elseif({in1, in2, in3} == 3'b100)

out = 8'b0001_0000;

elseif({in1, in2, in3} == 3'b101)

out = 8'b0010_0000;

elseif({in1, in2, in3} == 3'b110)

out = 8'b0100_0000;

elseif({in1, in2, in3} == 3'b111)

out = 8'b1000_0000;

else

out = out;//输出变量赋值给自己

|

31 endmodule

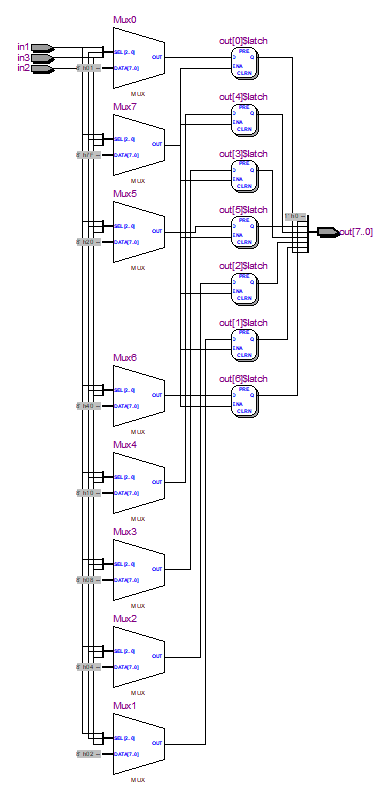

根据上面RTL代码综合出的RTL视图如图 14‑5所示,我们可以看到产生了Latch。

图 14‑5 RTL视图(三)

情况三:组合逻辑中输出变量赋值给自己(二)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 | module latch_three

(

input wire in1 , //输入信号in1

input wire in2 , //输入信号in2

input wire in3 , //输入信号in2

output reg [7:0] out //输出信号out

);

//out:根据3个输入信号选择输出对应的8bit out信号

always@(*)

case({in1, in2, in3})

3'b000 : out = 8'b0000_0001;

3'b001 : out = 8'b0000_0010;

3'b010 : out = 8'b0000_0100;

3'b011 : out = 8'b0000_1000;

3'b100 : out = 8'b0001_0000;

3'b101 : out = 8'b0010_0000;

3'b110 : out = 8'b0100_0000;

3'b111 : out = out; //输出变量赋值给自己

default: out = 8'b0000_0001;

endcase

endmodule

|

根据上面RTL代码综合出的RTL视图如图 14‑6所示,我们可以看到也产生了Latch。

图 14‑6 RTL视图(四)

8.5. 章末总结¶

本章重点讲解了Latch是什么、产生的原因以及如何避免Latch的产生,我们为大家进行了总结,大家一定要记住:在组合逻辑中一定要避免输出信号处于不定的状态,一定要让输出无论在任何条件下都有一个已知的状态,就可以避免Latch的产生。Latch作为一种基本电路单元,会影响到电路的时序性能,应尽量避免使 用,但出现Latch造成设计与意图不符的情况,是由于设计人员代码不规范造成的。但也随着综合器越来越优化使之可以更精准的识别出该代码是否为设计者真正想要的Latch,并给出必要的提示。