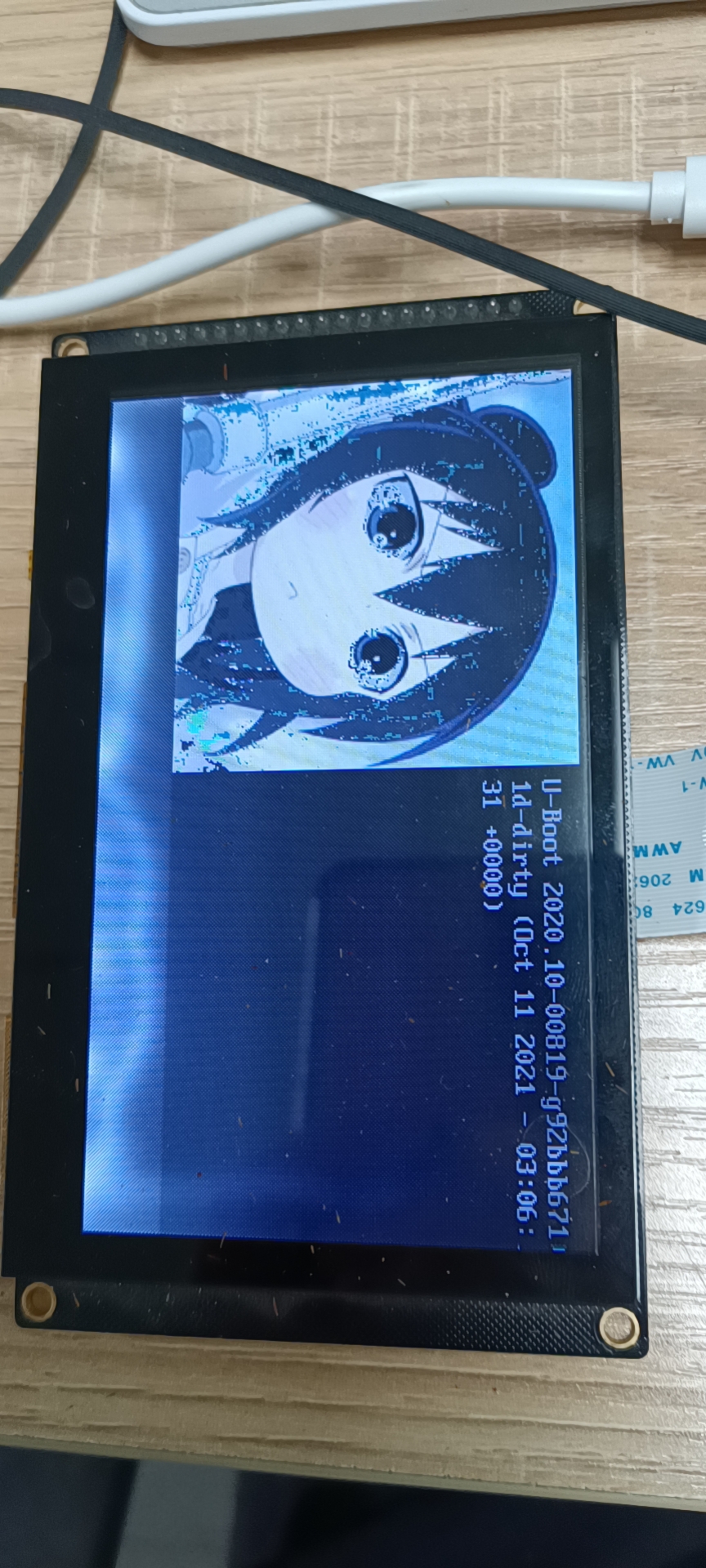

3. 修改Uboot开机logo¶

3.1. 简介¶

开机LOGO即是上电LOGO,因为UBOOT的启动时间较短显示的LOGO存在时间也较短,现在大部分使用的是Linux内核启动Logo,但为了教程的严谨性,我还是讲解一下Uboot的开机LOGO。

如需更实用的参考本教程下面的章节 修改Linux内核启动Logo

由于NXP官方在近几年的Uboot版本不提供LOGO显示功能,所以需要自己配置LCD引脚和驱动,由于找遍全网也没详细的教程,以下内容为本人摸索得出,如有错误欢迎指正。

3.2. 下载安装编译镜像系统¶

使用平台:Ubuntu 18.04.5 LTS 版本

可以使用我们提供的虚拟机镜像 https://doc.embedfire.com/products/link/zh/latest/linux/ebf_i.mx6ull.html#id4

也可以自己下载ubuntu 18.04.5 LTS官方镜像搭建

https://mirrors.aliyun.com/ubuntu-releases/bionic/ubuntu-18.04.5-desktop-amd64.iso

3.3. 安装编译工具和依赖¶

使用apt工具能快速安装好我们需要的工具和依赖

1 | sudo apt install make git gcc-arm-none-eabi gcc bison flex libssl-dev dpkg-dev lzop libncurses5-dev

|

3.4. 下载Uboot源代码¶

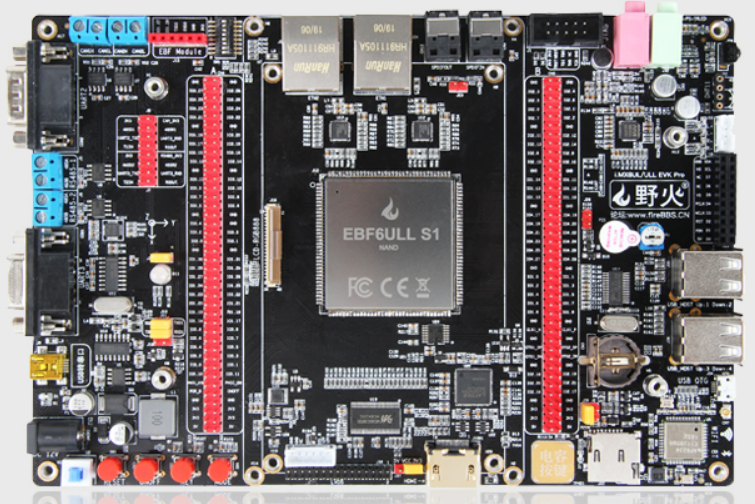

可以到我们的gitee上下载我们的源码,也可以下载NXP官方的源码进行配置,本教程就以我们野火修改过的Uboot进行讲解

我们的UBOOT地址:https://gitee.com/Embedfire/ebf_linux_uboot/tree/ebf_v2020_10_imx/

NXP官方的UBOOT地址:https://source.codeaurora.org/external/imx/uboot-imx/

1 2 3 4 5 | #获取野火uboot

git clone -b ebf_v2020_10_imx https://gitee.com/Embedfire/ebf_linux_uboot

#或者

git clone -b ebf_v2020_10_imx https://github.com/Embedfire/ebf_linux_uboot

|

3.5. 文件配置¶

3.5.1. 头文件¶

文件位置:include/configs/mx6ullfire.h

在该文件的末尾的endif前添加如下代码

1 2 3 4 5 6 | #define CONFIG_VIDEO_MXS

#define CONFIG_VIDEO_LOGO

#define CONFIG_SPLASH_SCREEN

#define CONFIG_SPLASH_SCREEN_ALIGN

#define CONFIG_VIDEO_BMP_LOGO

#define MXS_LCDIF_BASE MX6UL_LCDIF1_BASE_ADDR

|

CONFIG_VIDEO_MXS:定义了LCD的引脚和初始化

CONFIG_VIDEO_LOGO:定义了video_logo的一些封装函数

CONFIG_SPLASH_SCREEN:定义了LCD的初始化函数

CONFIG_SPLASH_SCREEN_ALIGN:定义了和屏幕对齐的函数

CONFIG_VIDEO_BMP_LOGO:定义了BMP文件格式支持函数

MXS_LCDIF_BASE MX6UL_LCDIF1_BASE_ADDR:定义了LCD的基地址:0x021C8000

3.5.2. 配置文件¶

根据自己的板型选择设置

EMMC的配置文件(包含SD卡):/root/uboot/mx6ull_fire_mmc_defconfig

nand的配置文件:/root/uboot/mx6ull_fire_nand_defconfig

在文件末尾加上

1 2 | CONFIG_CMD_BMP=y

CONFIG_VIDEO=y

|

CONFIG_CMD_BMP:使能了BMP调用命令

CONFIG_VIDEO:开启VIDEO功能

3.5.3. 单板文件¶

文件位置:board/freescale/mx6ullfire/mx6ullfire.c

该文件添加的内容较多,具体详看代码

若代码复制不方面可以直接下载源码文件进行替换 mx6ullfire.c

其中以//—-1–开头,以//—-2–结尾则为添加的内容

3.6. 编译¶

1 2 3 4 | make distclean

make mx6ull_fire_mmc_defconfig CROSS_COMPILE=arm-none-eabi-

#编译uboot

make CROSS_COMPILE=arm-none-eabi- -j4

|

3.7. 烧录启动¶