4. 开发平台介绍¶

本章主要讲解如何使用i.MX RT驱动其ETH章节的讲解,讲解好了基础外设,以便后面章节讲解LwIP移植时对接底层接口。在学习本章的过程中,可以参考我们出版的书籍《STM32库开发实战指南》中的 以太网 章节。

4.1. 以太网简介¶

以太网(Ethernet)是互联网技术的一种,由于它是在组网技术中占的比例最高,很多人直接把以太网理解为互联网。

以太网是指遵守 IEEE 802.3 标准组成的局域网,由 IEEE 802.3 标准规定的主要是位于参考模型的物理层(PHY)和数据链路层中的介质访问控制子层(MAC)。在家庭、企业和学校所组建的 PC 局域网形式一般也是以太网,其标志是使用水晶头网线来连接(当然还有其它形式)。 IEEE 还有其它局域网标准,如 IEEE 802.11 是无线局域网,俗称 Wi-Fi。 IEEE802.15 是个人域网,即蓝牙技术,其中的 802.15.4 标准则是 ZigBee 技术。

现阶段,工业控制、环境监测、智能家居的嵌入式设备产生了接入互联网的需求,利用以太网技术,嵌入式设备可以非常容易地接入到现有的计算机网络中。

4.1.1. PHY层¶

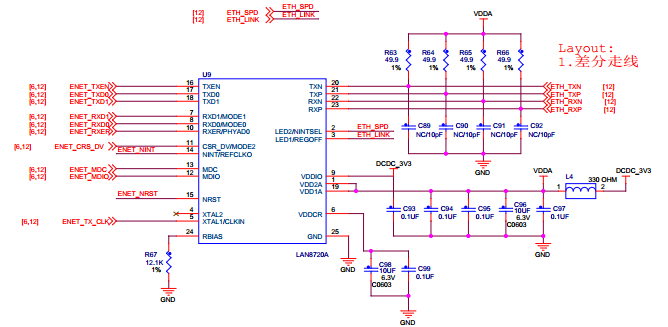

在物理层,由 IEEE 802.3 标准规定了以太网使用的传输介质、传输速度、数据编码方式和冲突检测机制,物理层一般是通过一个 PHY 芯片实现其功能的,我们使用的是野火i.MX RT系列开发板,板载的PHY芯片是LAN8720A。

4.1.1.1. 传输介质¶

传输介质包括同轴电缆、双绞线(水晶头网线是一种双绞线)、光纤。根据不同的传输速度和距离要求,基于这三类介质的信号线又衍生出很多不同的种类。最常用的是“五类线”适用于 100BASE-T 和 10BASE-T 的网络,它们的网络速率分别为 100Mbps 和 10Mbps。

4.1.1.2. 编码¶

为了让接收方在没有外部时钟参考的情况也能确定每一位的起始、结束和中间位置,在传输信号时不直接采用二进制编码。在 10BASE-T 的传输方式中采用曼彻斯特编码,在100BASE-T 中则采用 4B/5B 编码。

曼彻斯特编码把每一个二进制位的周期分为两个间隔,在表示“1”时,以前半个周期为高电平,后半个周期为低电平。表示“0”时则相反,具体见 图3_1。

图 3‑1曼彻斯特编码

采用曼彻斯特码在每个位周期都有电压变化,便于同步。但这样的编码方式效率太低,只有 50%。

在 100BASE-T 采用的 4B/5B 编码是把待发送数据位流的每 4 位分为一组,以特定的 5位编码来表示, 这些特定的 5 位编码能使数据流有足够多的跳变,达到同步的目的,而且效率也从曼彻斯特编码的 50%提高到了 80%。

4.1.1.3. CSMA/CD 冲突检测¶

早期的以太网大多是多个节点连接到同一条网络总线上(总线型网络),存在信道竞争问题,因而每个连接到以太网上的节点都必须具备冲突检测功能。以太网具备 CSMA/CD冲突检测机制,如果多个节点同时利用同一条总线发送数据,则会产生冲突,总线上的节点可通过接收到的信号与原始发送的信号的比较检测是否存在冲突,若存在冲突则停止发送数据,随机等待一段时间再重传。

现在大多数局域网组建的时候很少采用总线型网络,大多是一个设备接入到一个独立的路由或交换机接口,组成星型网络,不会产生冲突。但为了兼容,新出的产品还是带有冲突检测机制。

4.1.2. MAC子层¶

4.1.2.1. MAC的功能¶

MAC 子层是属于数据链路层的下半部分,它主要负责与物理层进行数据交接,如是否可以发送数据,发送的数据是否正确,对数据流进行控制等。它自动对来自上层的数据包加上一些控制信号,交给物理层。接收方得到正常数据时,自动去除 MAC 控制信号,把该数据包交给上层。

4.1.2.2. MAC 数据包¶

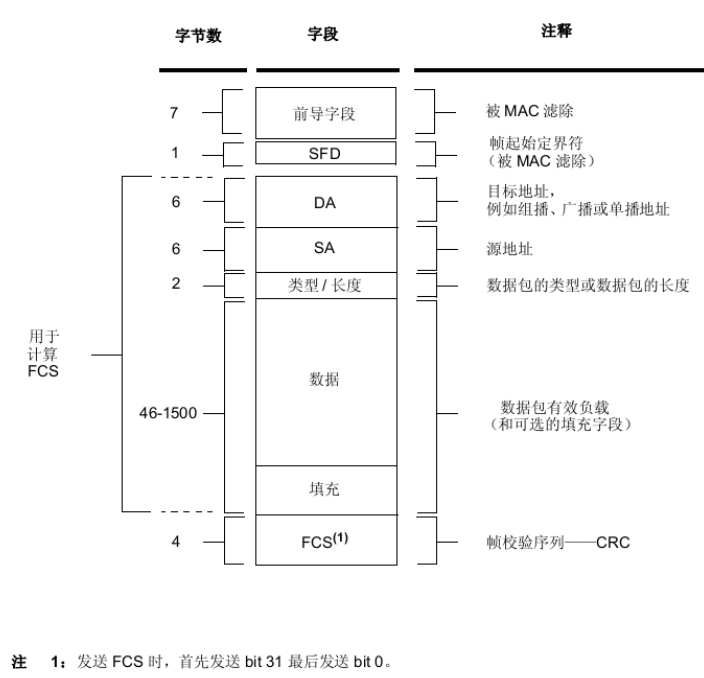

IEEE 对以太网上传输的数据包格式也进行了统一规定,见 图3_2。该数据包被称为MAC 数据包。

图 3‑2 MAC 数据包格式

MAC 数据包由前导字段、帧起始定界符、目标地址、源地址、数据包类型、数据域、填充域、校验和域组成。

前导字段,也称报头,这是一段方波,用于使收发节点的时钟同步。内容为连续 7 个字节的 0x55。字段和帧起始定界符在 MAC 收到数据包后会自动过滤掉。

帧起始定界符(SFD): 用于区分前导段与数据段的,内容为 0xD5。

MAC 地址: MAC 地址由 48 位数字组成,它是网卡的物理地址,在以太网传输的最底层,就是根据 MAC 地址来收发数据的。部分 MAC 地址用于广播和多播,在同一个网络里不能有两个相同的 MAC 地址。 PC 的网卡在出厂时已经设置好了 MAC 地址,但也可以通过一些软件来进行修改,在嵌入式的以太网控制器中可由程序进行配置。数据包中的 DA 是目标地址, SA 是源地址。

数据包类型: 本区域可以用来描述本 MAC 数据包是属于 TCP/IP 协议层的 IP 包、 ARP包还是 SNMP 包,也可以用来描述本 MAC 数据包数据段的长度。 如果该值被设置大于 0x0600,不用于长度描述,而是用于类型描述功能,表示与以太网帧相关的 MAC客户端协议的种类。

数据段: 数据段是 MAC 包的核心内容,它包含的数据来自 MAC 的上层。其长度可以从 0~1500 字节间变化。

填充域:由于协议要求整个 MAC 数据包的长度至少为 64 字节(接收到的数据包如果少于 64 字节会被认为发生冲突,数据包被自动丢弃),当数据段的字节少于 46 字节时,在填充域会自动填上无效数据,以使数据包符合长度要求。

校验和域: MAC 数据包的尾部是校验和域,它保存了 CRC 校验序列,用于检错。

以上是标准的 MAC 数据包, IEEE 802.3 同时还规定了扩展的 MAC 数据包,它是在标准的 MAC 数据包的 SA 和数据包类型之间添加 4 个字节的 QTag 前缀字段,用于获取标志的 MAC 帧。前 2 个字节固定为 0x8100,用于识别 QTag 前缀的存在;后两个字节内容分别为 3 个位的用户优先级、 1 个位的标准格式指示符(CFI)和一个 12 位的 VLAN 标识符。

4.2. i.MX RT的ENET外设¶

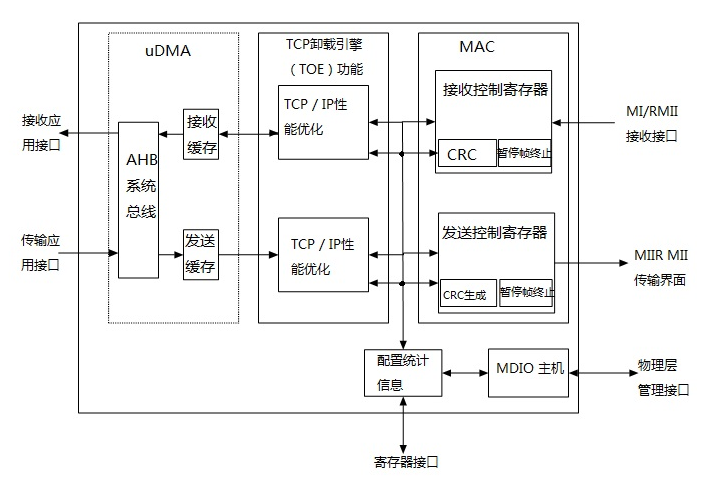

i.MX RT系列控制器内部集成了一个以太网外设,它实际是一个通过 DMA 控制器进行介质访问控制(MAC),它的功能就是实现 MAC 层的任务。借助以太网外设,i.MX RT控制器可以通过 ENET外设按照 IEEE 802.3-2002 标准发送和接收 MAC 数据包。

ENET内部自带专用的 DMA 控制器用于 MAC, ENET支持两个工业标准接口介质独立接口(MII)和简化介质独立接口(RMII)用于与外部 PHY 芯片连接。 MII 和 RMII 接口用于 MAC数据包传输。

物理层定义了以太网使用的传输介质、传输速度、数据编码方式和冲突检测机制,PHY 芯片是物理层功能实现的实体,生活中常用水晶头网线+水晶头插座+PHY 组合构成了物理层。

ENET有专用的 uDMA 控制器, 他通过AHB系统总线与内核和存储器相连,AHB总线接口主要负责接收和传输数据,通过DMA将其数据进行缓存,使用自带的TCP卸载引擎(TOE)功能来优化TCP/IP的性能,在进行数据发送是,先将数据有存储器以 DMA 传输到发送 TX FIFO 进行缓冲,然后由 MAC 内核发送; 接收数据时, RX FIFO 先接收以太网数据帧,再由 DMA 传输至存储器。

图 3‑3 ETH 功能框图

4.3. ENET信号引脚介绍¶

ENET_MDC:串行输出以太网数据。仅在发送断言期间有效。 MII/RMII/RGMII 接口都有该线。

ENET_MDIO:在外部phy和媒体访问控制器之间传输控制信息。数据是与MDC同步。此信号是复位后的输入。MII/RMII/RGMII 接口都有该线。

ENET_TX_DATA0: 串行输出以太网数据。仅在发送断言期间有效。MII/RMI有该线。

ENET_TX_DATA1: 串行输出以太网数据。仅在发送断言期间有效。MII/RMI有该线。

ENET_TX_DATA2: 串行输出以太网数据。仅在发送断言期间有效。MII有该线。

ENET_TX_DATA3: 串行输出以太网数据。仅在发送断言期间有效。MII有该线。

ENET_TX_ER: 当对一个或多个时钟周期进行断言而同时也对TXEN进行断言时,phy发送一个或多个非法符号。MII/RMI有该线。

ENET_TX_EN: 当对一个或多个时钟周期进行断言而同时也对TXEN进行断言时,phy发送一个或多个非法符号。MII/RMI有该线。

ENET_TX_CLK: 在MII模式下输入时钟,为TX_EN、TX_DATA[3:0]和TX_ER提供定时参考。以RGMII模式,提供外部125MHZ参考时钟输入。MII/RMI有该线。

ENET_RX_DATA0: 包含以太网输入数据当RX_EN被断言时,从PHY传输mediaaccess控制器。MII/RMI有该线。

ENET_RX_DATA1: 包含以太网输入数据当RX_EN被断言时,从PHY传输mediaaccess控制器。MII/RMI有该线。

ENET_RX_DATA3: 包含以太网输入数据当RX_EN被断言时,从PHY传输mediaaccess控制器。MII有该线。

ENET_RX_DATA2: 包含以太网输入数据当RX_EN被断言时,从PHY传输mediaaccess控制器。MII有该线。

ENET_RX_ER: 当使用RXDV断言时,指示PHY在当前帧中检测到错误。MII/RMI有该线。

ENET_RX_EN: 断言此输入表示PHY在MII上存在有效的半字节。RX_EN必须从到最后一个半字节的帧。断言RX必须不迟于SFD开始,并排除任何EOF。在RMII模式下,这个PIN还生成CRS信号。MII/RMI有该线。

ENET_RX_CLK: 在MII模式下输入时钟,为TX_EN、TX_DATA[3:0]和TX_ER提供定时参考。以RGMII模式,提供外部125MHZ参考时钟输入。MII有该线。

ENET_CRS: 载波感应。断言时,表示传输或接收介质未空闲。在RMII模式下,此信号出现在RMII_CRS_DV引脚。MII有该线。

ENET_COL: 在检测到碰撞时断言并保持断言当碰撞持续的时候。此信号未定义为全双工模式。MII有该线。

ENET_REF_CLK: 在RMII模式下,该信号是接收、发送和控制接口的参考时钟。RMII有该线。

ENET_1588EVENT0_OUT: 捕获/比较块输入/输出事件总线信号。当配置为捕获并检测到上升沿时,当前计时器值被锁定并传输到相应的ENET-TCCRN登记簿软件。当配置为比较时,对应的当计时器达到中编程的比较值注册ENET。中断或DMA请求可以是如果设置了ENET TCSRN[TIE]或ENET TCSRN[TDRE]中的相应位,则触发。

ENET_1588_EVENT0_OUT有一个可编程的输出宽度,见IOMUXC_GPR0[CLK_STRETCH],相对于所有其他事件输出信号延迟一个时钟周期。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT0_IN: 捕获/比较块输入/输出事件总线信号。当配置为捕获并检测到上升沿时,当前计时器值被锁定并传输到相应的ENET-TCCRN登记簿软件。当配置为比较时,对应的当定时器达到寄存器中编程的比较值ENET_TCCRn。中断或DMA请求可以是如果ENET TCSRN[TIE]中的对应位触发或设置了ENET TCSRN[TDRE]。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT1_OUT:捕获/比较块输入/输出事件总线信号。当配置为捕获时,上升沿是检测到时, 当前定时器值被锁定并传输到相应的ENET_TCRN寄存器中,以便软件检查。当配置为比较时,对应的信号1588_事件被断言为1计时器达到比较值时循环在寄存器ENET中编程。如果ENET TCSRN[TIE]或ENET U TCSRN[TDRE]已设置。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT1_IN: 捕获/比较块输入/输出事件总线信号。当被配置为捕捉并检测到上升沿时,当前定时器值被锁定并传送到相应的ENET_TCRN寄存器中以供软件检查。当配置为比较时,为一个计时器达到比较值时循环在寄存器ENET中编程。安如果ENET TCSRN[TIE]或ENET U TCSRN[TDRE]已设置。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT2_OUT: 捕获/比较块输入/输出事件总线信号。当被配置为捕捉并检测到上升沿时,当前定时器值被锁定并传送到相应的ENET_TCRN寄存器中以供软件检查。当配置为比较时,当定时器达到在寄存器ENET_TCRN中编程的比较值时,对应的信号1588_EVENT被断言一个周期。如果设置了ENET TCSRN[TIE]或ENET TCSRN[TDRE]中的相应位,则可以触发中断或DMA请求。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT2_IN: 捕获/比较块输入/输出事件总线信号。当被配置为捕捉并检测到上升沿时,当前定时器值被锁定并传送到相应的ENET_TCRN寄存器中以供软件检查。当配置为比较时,当定时器达到在寄存器ENET_TCRN中编程的比较值时,对应的信号1588_EVENT被断言一个周期。如果设置了ENET TCSRN[TIE]或ENET TCSRN[TDRE]中的相应位,则可以触发中断或DMA请求。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT3_OUT: 捕获/比较块输入/输出事件总线信号。当被配置为捕捉并检测到上升沿时,当前定时器值被锁定并传送到相应的ENET_TCRN寄存器中以供软件检查。当配置为比较时,当定时器达到在寄存器ENET_TCRN中编程的比较值时,对应的信号1588_EVENT被断言一个周期。如果设置了ENET TCSRN[TIE]或ENET TCSRN[TDRE]中的相应位,则可以触发中断或DMA请求。MII/RMII/RGMII 接口都有该线。

ENET_1588EVENT3_IN: 捕获/比较块输入/输出事件总线信号。当配置为捕获并检测到上升沿时,当前计时器值被锁存并传送到相应的ENET TCCRN寄存器中,以供软件检查。当配置为比较时,当定时器达到在寄存器ENET_TCRN中编程的比较值时,对应的信号1588_EVENT被断言一个周期。如果设置了ENET TCSRN[TIE]或ENET TCSRN[TDRE]中的相应位,则可以触发中断或DMA请求。MII/RMII/RGMII 接口都有该线。

4.4. PHY:LAN8720A¶

LAN8720A 是 SMSC 公司(已被 Microchip 公司收购)设计的一个体积小、功耗低、全能型 10/100Mbps 的以太网物理层收发器。它是针对消费类电子和企业应用而设计的。LAN8720A 总共只有 24Pin,仅支持 RMII 接口。由它组成的网络结构见 图3_4。

图 3‑4由 LAN8720A 组成的网络系统结构

LAN8720A 通过 RMII 与 MAC 连接。 RJ45 是网络插座,在与 LAN8720A 连接之间还需要一个变压器,所以一般使用带电压转换和 LED 指示灯的 HY911105A 型号的插座。一般来说,必须为使用 RMII 接口的 PHY 提供 50MHz 的时钟源输入到 REF_CLK 引脚,不过LAN8720A 内部集成 PLL,可以将 25MHz 的时钟源陪频到 50MHz 并在指定引脚输出该时钟,所以我们可以直接使其与 REF_CLK 连接达到提供 50MHz 时钟效果。

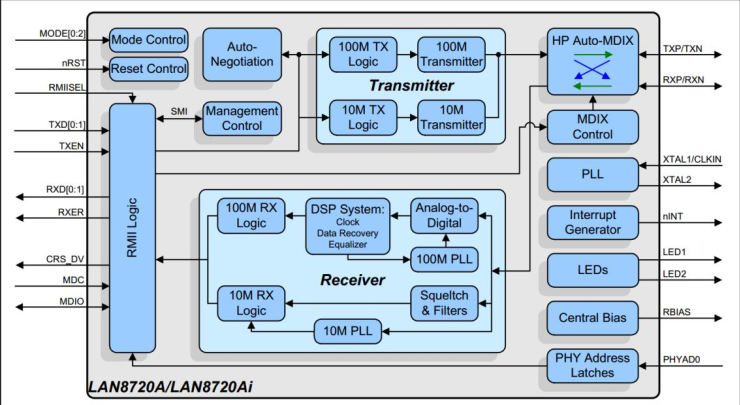

LAN8720A 内部系统结构见 图3_5。

图 3‑5LAN8720A 内部系统结构

LAN8720A 有各个不同功能模块组成,最重要的要数接收控制器和发送控制器,其它的基本上都是与外部引脚挂钩,实现信号传输。部分引脚是具有双重功能的,比如PHYAD0 与 RXER 引脚是共用的,在系统上电后 LAN8720A 会马上读取这部分共用引脚的电平,以确定系统的状态并保存在相关寄存器内,之后则自动转入作为另一功能引脚。

PHYAD[0]引脚用于配置 SMI 通信的 LAN8720A 地址,在芯片内部该引脚已经自带下拉电阻,默认认为 0(即使外部悬空不接),在系统上电时会检测该引脚获取得到 LAN8720A的地址为 0 或者 1,并保存在特殊模式寄存器(R18)的 PHYAD 位中,该寄存器的 PHYAD有 5 个位,在需要超过 2 个 LAN8720A 时可以通过软件设置不同 SMI 通信地址。PHYAD[0]是与 RXER 引脚共用。

MODE[2:0]引脚用于选择 LAN8720A 网络通信速率和工作模式,可选 10Mbps 或100Mbps 通信速度,半双工或全双工工作模式,另外 LAN8720A 支持 HP Auto-MDIX 自动翻转功能,即可自动识别直连或交叉网线并自适应。一般将 MODE 引脚都设置为 1,可以让 LAN8720A 启动自适应功能,它会自动寻找最优工作方式。 MODE[0]与 RXD0 引脚共用、MODE[1]与 RXD1 引脚共用、 MODE[2]与 CRS_DV 引脚共用。

nINT/REFCLKO 引脚用于 RMII 接口中 REF_CLK 信号线,当 nINTSEL 引脚为低电平是,它也可以被设置成 50MHz 时钟输出,这样可以直接与 STM32F42x 的 REF_CLK 引脚连接为其提供 50MHz 时钟源,这种模式要求为 XTAL1 与 XTAL2 之间或为 TAL1/CLKIN提供 25MHz 时钟,由 LAN8720A 内部 PLL 电路陪频得到 50MHz 时钟,此时nIN/REFCLKO 引脚的中断功能不可用,用于 50MHz 时钟输出。当 nINTSEL 引脚为高电平时,LAN8720A 被设置为时钟输入,即外部时钟源直接提供 50MHz 时钟接入 STM32F42x的 REF_CLK 引脚和 LAN8720A 的 XTAL1/CLKIN 引脚,此时INT/REFCLKO 可用于中断功能。 nINTSEL 与 LED2 引脚共用,一般使用下拉。

REGOFF 引脚用于配置内部+1.2V 电压源, LAN8720A 内部需要+1.2V 电压,可以通过VDDCR 引脚输入+1.2V 电压提供,也可以直接利用 LAN8720A 内部+1.2V 稳压器提供。当REGOFF 引脚为低电平时选择内部+1.2V 稳压器。 REGOFF 与 LED1 引脚共用。

SMI 支持寻址 32 个寄存器, LAN8720A 只用到其中 14 个,参考 图3_6。

图 3‑6LAN8720A 寄存器列表

序号与 SMI 数据帧中的 RADDR 是对应的,这在编写驱动时非常重要,本文将它们标记为 R0~R31。寄存器可规划为三个组: Basic、 Extended 和 Vendor-specific。Basic 是IEEE802.3 要求的, R0 是基本控制寄存器,其位 15 为 Soft Reset 位,向该位写 1 启动LAN8720A 软件复位,还包括速度、自适应、低功耗等等功能设置。 R1 是基本状态寄存器。Extended 是扩展寄存器,包括 LAN8720A 的 ID 号、制造商、版本号等等信息。Vendorspecific 是供应商自定义寄存器, R31 是特殊控制/状态寄存器,指示速度类型和自适应功能。