15. RA系列MCU中断应用概览¶

本章配套视频介绍:

《19-RA系列MCU中断应用概览(第1节)——ICU框图分析》

https://www.bilibili.com/video/BV1oG411v77x/

《20-RA系列MCU中断应用概览(第2节)——NVIC简介》

https://www.bilibili.com/video/BV1Sj411s73P/

《21-RA系列MCU中断应用概览(第3节)——RA6M5中断概览》

https://www.bilibili.com/video/BV1Pg4y117xi/

本章参考资料:《RA6M5 Group User’s Manual: Hardware》 主要参考章节:13. Interrupt Controller Unit (ICU)、18. Event Link Controller (ELC)

15.1. ICU简介¶

这里的ICU可不是重症加强护理病房ICU(Intensive Care Unit),这里的ICU是中断控制单元Interrupt Controller Unit。

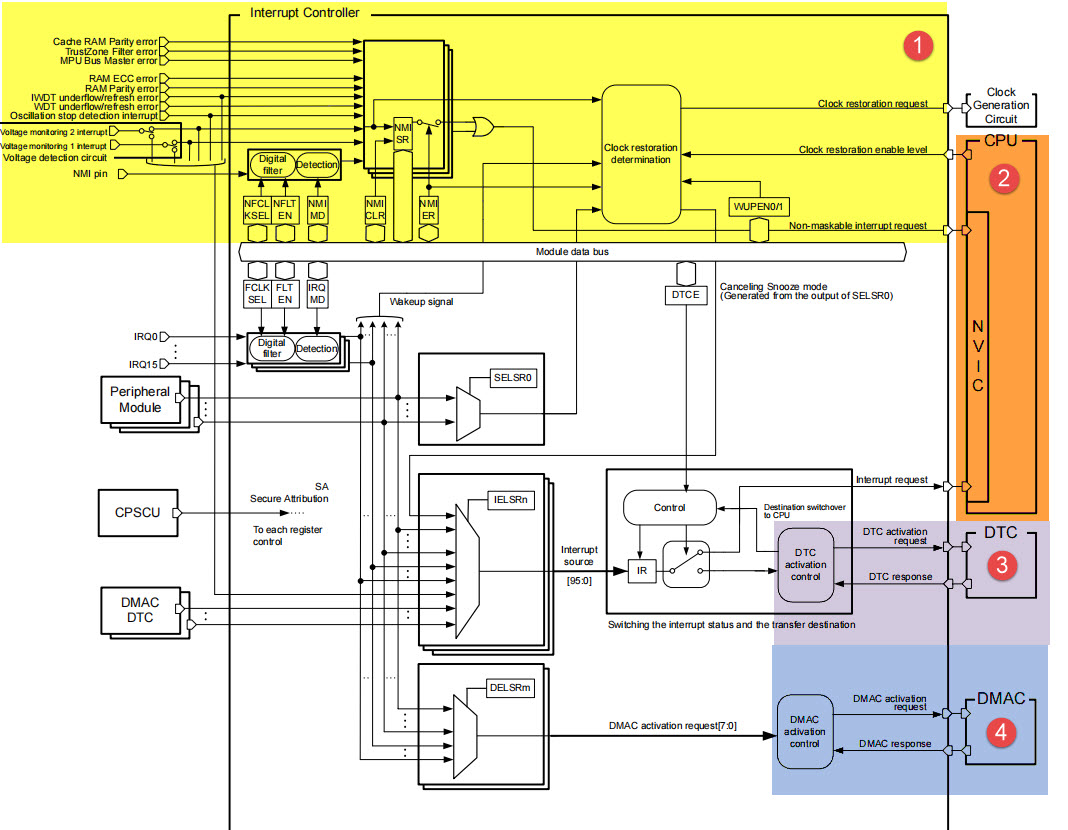

中断控制器单元(ICU)控制着一些事件发出的信号,从而链接到嵌套矢量中断控制器(NVIC)、DMA控制器(DMAC)和数据传输控制器(DTC)模块。ICU还控制着不可屏蔽的中断。 所以可以说围绕着 ICU 的有四个部分:NVIC、DMAC、DTC和NMI。

15.1.1. ICU框图分析¶

模块1 |

NMI |

不可屏蔽的中断 |

模块2 |

NVIC |

嵌套向量中断控制器 |

模块3 |

DTC |

数据传输控制器 |

模块4 |

DMAC |

直接内存访问控制器 |

其中在ICU里最重要的是NVIC,它是属于内核级别的中断控制器。其次是DTC,用于提供在被中断请求激活时传输数据的功能。之后是DMAC,当产生DMA传输请求时,DMAC将存储在传输源地址的数据传输到传输目的地地址。最后是NMI不可屏蔽中断NonMaskable,用于处理非常紧急的事件。

15.2. DMAC与DTC¶

Direct memory access controller (DMAC) - 直接存储区访问控制器以及Data Transfer Controller (DTC) - 数据传输控制器。其主要功能都是用来搬数据, 但是不需要占用CPU的运行,即在传输数据的时候,CPU 可以干其他的事情,好像是多线程一样。 数据传输支持从外设到存储器或者存储器到存储器,这里的存储器可以是 SRAM 或者是 FLASH。

注解

这两部分会在第20章进行详细的讲解,这里将不再赘述。

15.3. NVIC简介¶

NVIC 英文名全称:(Nested Vector Interrupt Controller)中文名:嵌套向量中断控制。 在所有Cortex-M系列处理器中都包含了一个叫做 NVIC 模块,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。但是各个芯片厂商在设计芯片的时候会对Cortex-M系列的内核里面的NVIC进行裁剪。

NVIC能够处理系统异常比如复位和一些系统错误,NVIC还能够处理中断源,比如定时器中断、外部中断等。

15.3.1. NVIC异常类型¶

RA系列MCU在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。其中系统异常有8个(如果把Reset和HardFault也算上的话就是10个)。 除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。 有关具体的系统异常和外部中断可在core_cm33.h这个头文件查询到,在IRQn_Type这个结构体里面包含了RA系列MCU全部的异常声明。

表格 15‑1 NVIC异常清单

编号 |

优先级 |

优先级类型 |

名称 |

说明 |

地址 |

保留(实际存的是MSP地址) |

0X0000 0000 |

||||

-3 |

固定 |

Reset |

复位 |

0X0000 0004 |

|

-2 |

固定 |

NMI |

不可屏蔽中断。 RCC 时钟安全系统 (CSS) 连接到 NMI 向量 |

0X0000 0008 |

|

-1 |

固定 |

HardFault |

所有类型的错误 |

0X0000 000C |

|

0 |

可编程 |

MemManage |

存储器管理 |

0X0000 0010 |

|

1 |

可编程 |

BusFault |

预取指失败,存储器访问失败 |

0X0000 0014 |

|

2 |

可编程 |

UsageFault |

未定义的指令或非法状态 |

0X0000 0018 |

|

保留 |

0X0000 001C-0X0000 002B |

||||

3 |

可编程 |

SVCall |

通过 SWI 指令调用的系统服务 |

0X0000 002C |

|

4 |

可编程 |

Debug Monitor |

调试监控器 |

0X0000 0030 |

|

保留 |

0X0000 0034 |

||||

5 |

可编程 |

PendSV |

可挂起的系统服务 |

0X0000 0038 |

|

6 |

可编程 |

SysTick |

系统嘀嗒定时器 |

0X0000 003C |

15.3.2. NVIC寄存器简介¶

中断向量嵌套控制器是用来管理所有中断和事件的,包括中断的使能和除能,中断的优先级。这个是属于内核的东西,相应的寄存器可参考代码15-1和表NVIC寄存器。

typedef struct

{

__IOM uint32_t ISER[16U]; // 中断使能寄存器

uint32_t RESERVED0[16U];

__IOM uint32_t ICER[16U]; //中断清除使能寄存器

uint32_t RSERVED1[16U];

__IOM uint32_t ISPR[16U]; //中断挂起寄存器

uint32_t RESERVED2[16U];

__IOM uint32_t ICPR[16U]; //中断清除挂起寄存器

uint32_t RESERVED3[16U];

__IOM uint32_t IABR[16U]; // 中断激活寄存器\中断有效位寄存器

uint32_t RESERVED4[16U];

__IOM uint32_t ITNS[16U]; //中断目标安全寄存器

uint32_t RESERVED5[16U];

__IOM uint8_t IPR[496U]; // 中断优先级寄存器

uint32_t RESERVED6[580U];

__OM uint32_t STIR;

} NVIC_Type;

在这里__OM是只能写入,__IOM是可读和可写。

寄存器名称 |

寄存器功能 |

寄存器英文名 |

|---|---|---|

ISER |

中断使能寄存器 |

Interrupt Set Enable register |

ICER |

中断清除使能寄存器 |

Interrupt Clear Enable Registers |

ISPR |

中断挂起寄存器 |

Interrupt Set Pending Registers |

ICPR |

中断清除挂起寄存器 |

Interrupt Clear Pending Registers |

IABR |

中断激活寄存器中断有效位寄存器 |

Interrupt Active Bit Registers |

ITNS |

中断目标安全寄存器 |

Interrupt Target Non-secure Registers |

IPR |

中断优先级寄存器 |

Interrupt Priority Registers |

15.3.3. NVIC 中断配置固件库¶

固件库文件core_cm33.h的最后,还提供了NVIC的一些函数,这些函数遵循CMSIS规则,只要是Cortex-M33 的处理器都可以使用,具体如下:

表格 15‑3 符合CMSIS标准的NVIC库函数

NVIC库函数 |

描述 |

void NVIC_EnableIRQ(IRQn_Type IRQn) |

使能中断 |

void NVIC_DisableIRQ(IRQn_Type IRQn) |

禁止中断 |

void NVIC_SetPendingIRQ(IRQn_Type IRQn) |

设置中断挂起位 |

void NVIC_ClearPendingIRQ(IRQn_Type IRQn) |

清除中断挂起位 |

uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn) |

获取挂起中断编号 |

void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority) |

设置中断优先级 |

uint32_t NVIC_GetPriority(IRQn_Type IRQn) |

获取中断优先级 |

void NVIC_SystemReset(void) |

系统复位 |

这些库函数我们在编程的时候用的都比较少,甚至基本都不用。在配置中断的时候我们还有更简洁的方法,请看中断编程小节。

15.4. RA6M5¶

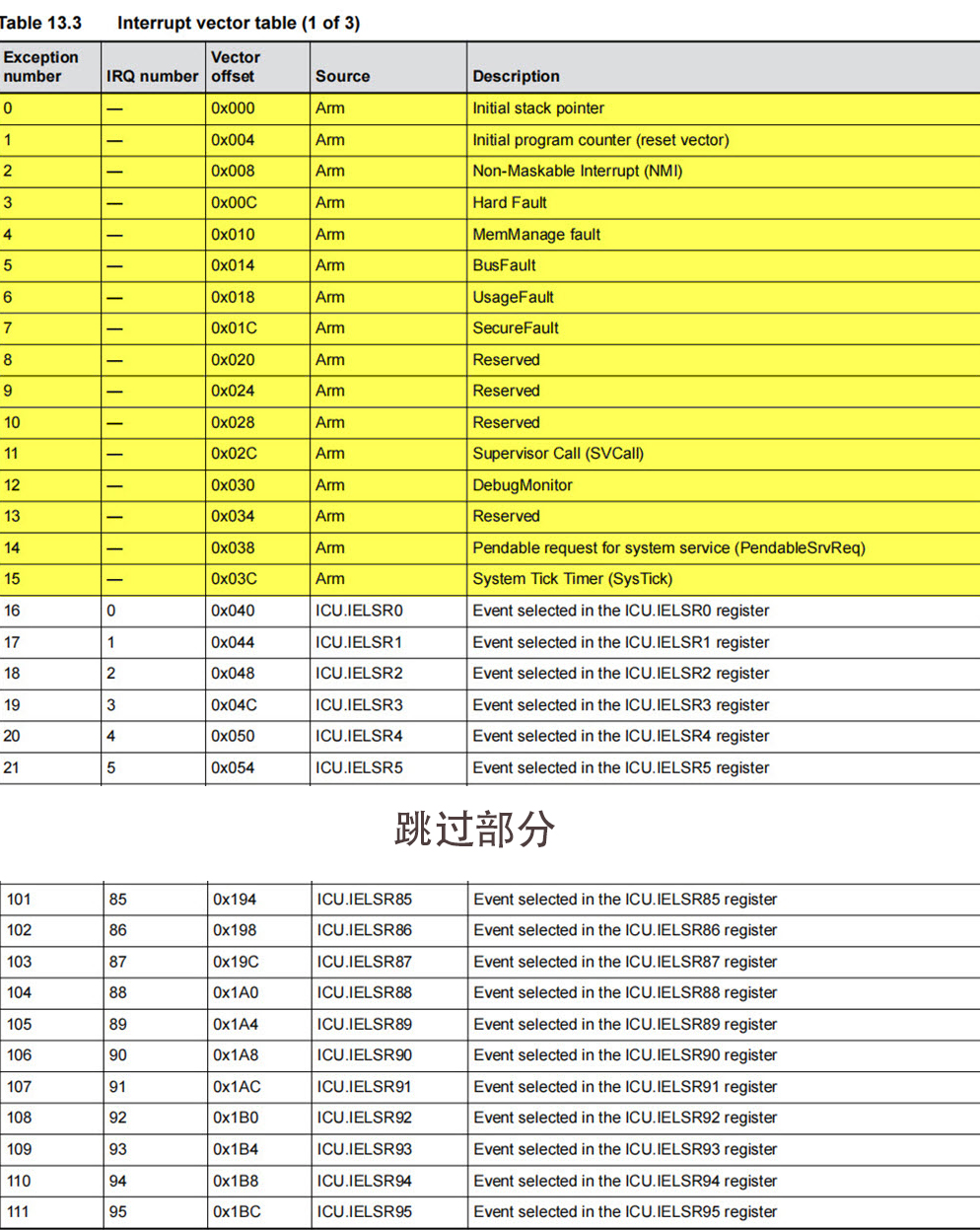

瑞萨的RA6M5采用了Cortex-M33内核,Cortex-M33内核的NVIC支持为数众多的系统异常和外部中断,除了个别异常的优先级被定死外,其它异常的优先级都是可配置的。 Cortex-M33可以配置的支持多达480个外部中断,瑞萨对于中断向量表的使用有112个,其中可配置的有96个, RA6M5外围模块的可配置的中断事件有287个,最高可达256个优先级。

15.4.1. 中断向量表¶

中断向量表提供了相应的中断服务程序,我们一般称它为ISR,中断响应通过提取中断服务程序首地址的方式来完成程序指针PC的跳转。 但是对于Cortex-M33的内核,RA6M5在中断向量表中使用了112个ISR。下面提供了瑞萨RA6M5对于ISR的使用。

注解

其中前16个是配置Arm的比如初始堆栈指针等为黄色的部分。后面96个是配置ICU事件选择寄存器ICU.IELSR。 具体可翻阅《RA6M5 Group User’s Manual: Hardware》里的Table 13.3 Interrupt vector table。

15.4.2. ICU.IELSRn寄存器¶

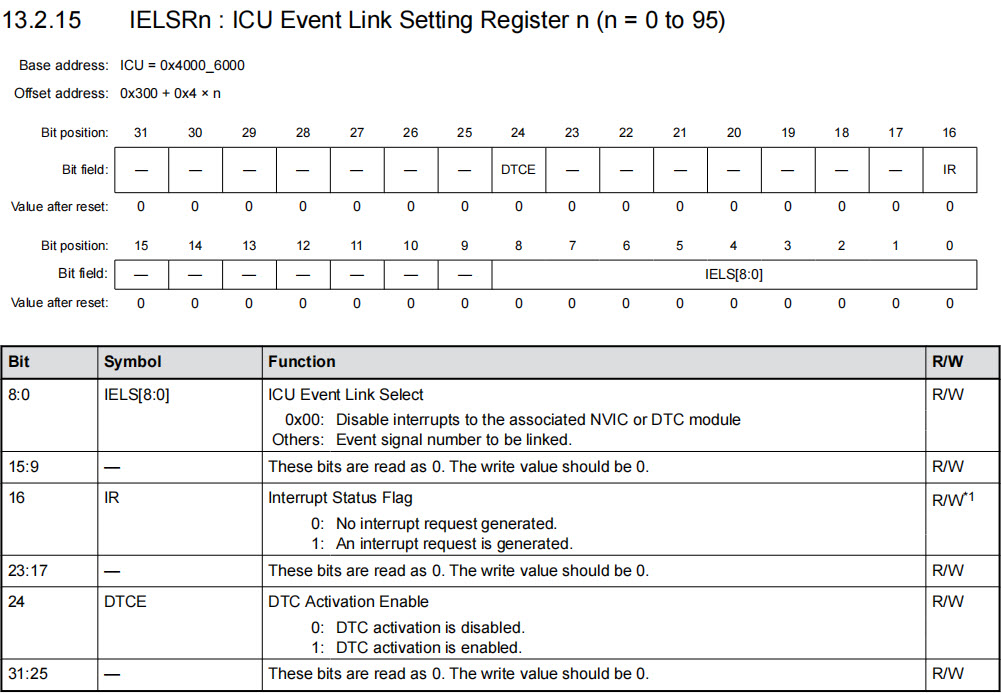

IELSRn寄存器选择NVIC使用的IRQi源。IELSRn对应于NVIC IRQ输入源编号,其中n=0至95。

IELS[8:0]位将事件信号链接到相关的NVIC或DTC模块。事件选项分为8组(组0至7)。 IR状态标志表示来自IELS[8:0]中指定事件的单个中断请求。 DTCE位是DTC激活使能位,当DTCE位设置为1时,相关事件被选择为DTC激活源。

15.4.3. 中断事件表¶

在中断事件表里,瑞萨RA6M5中可以配置什么中断,如IIC中断、GPT中断、Port中断、DMAC中断、DTC中断、AGT中断等等, 具体可翻阅《RA6M5 Group User’s Manual: Hardware》里的Table 13.4 Event table。

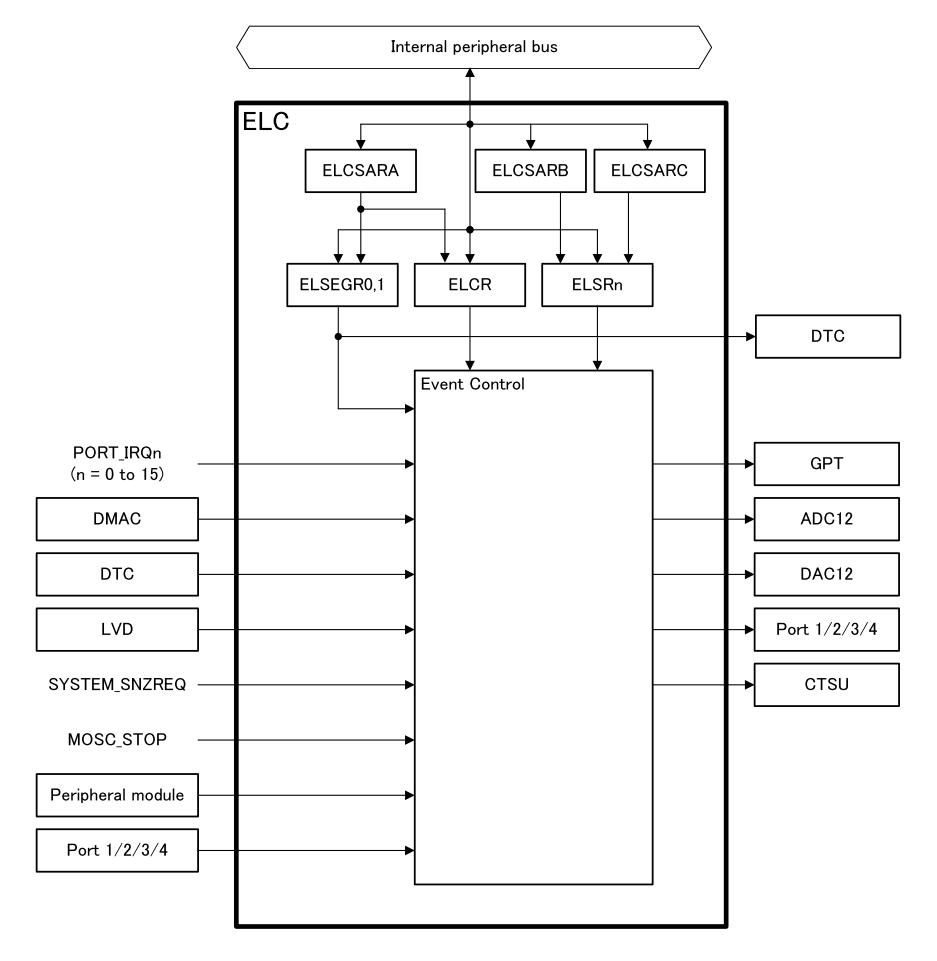

15.5. ELC 模块简介¶

事件链接控制器(Event Link Controller, ELC)将各种外围模块产生的事件请求作为源信号, 连接到不同的模块,允许模块之间直接链接,不需要CPU干预。 就是将事件(中断源)绑定到外设功能,当事件触发时,就会执行所绑定的外设功能。你可以认为这是一种中断,只不过这种中断不需要CPU的参与。

事件号和中断号之间的关系: 事件链接的事件号与相关联的中断源的事件号相同。

ELC 特性

219 种事件信号可以被直接连接到各个模块。ELC 生成 ELC 事件信号和激活 DTC 的事件。