3. 初识STM32MP157¶

本章参考资料:《dm00327659-stm32mp157-advanced-armbased-32bit-mpus-stmicroelectronics》参考手册、 《stm32mp157a》数据手册。

学习本章时,配合《dm00327659-stm32mp157-advanced-armbased-32bit-mpus-stmicroelectronics》参考手册 “2 Memory and bus architecture ”章节一起阅读,效果会更佳。

3.1. STM32MP157架构¶

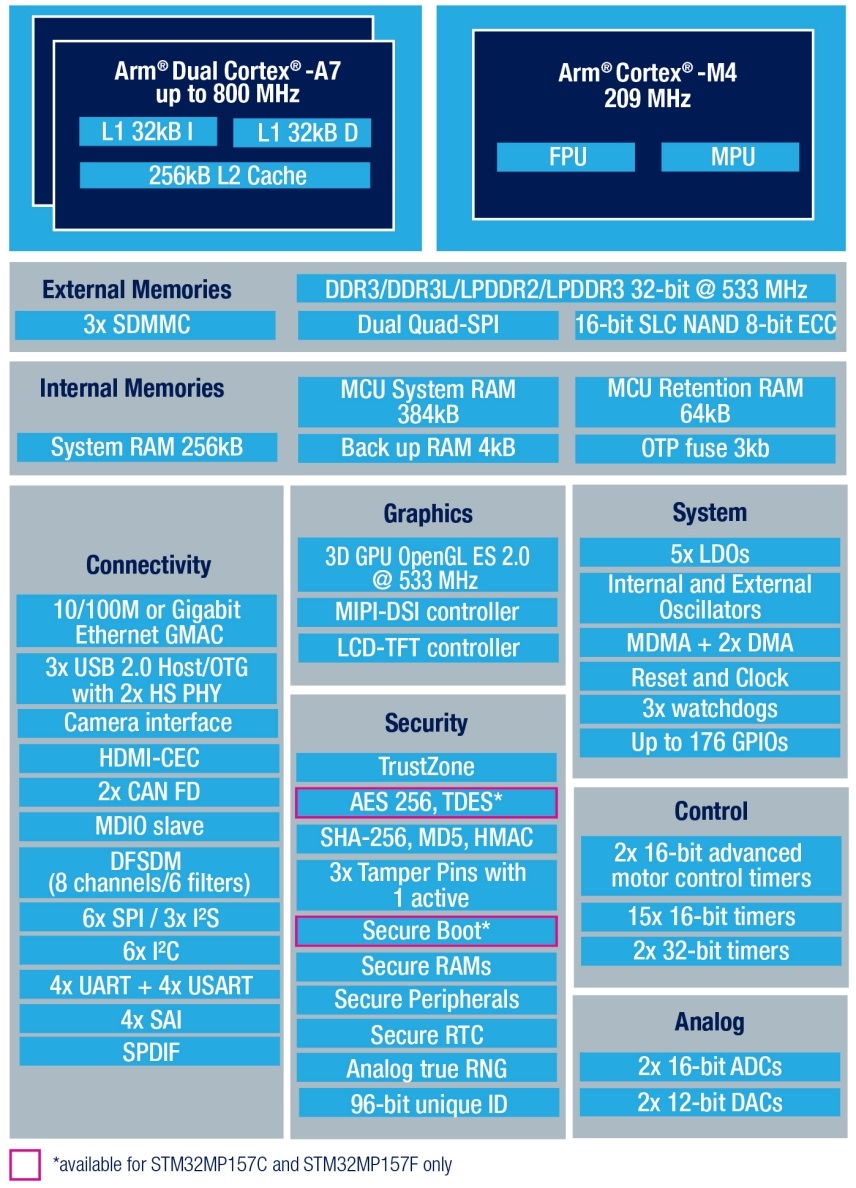

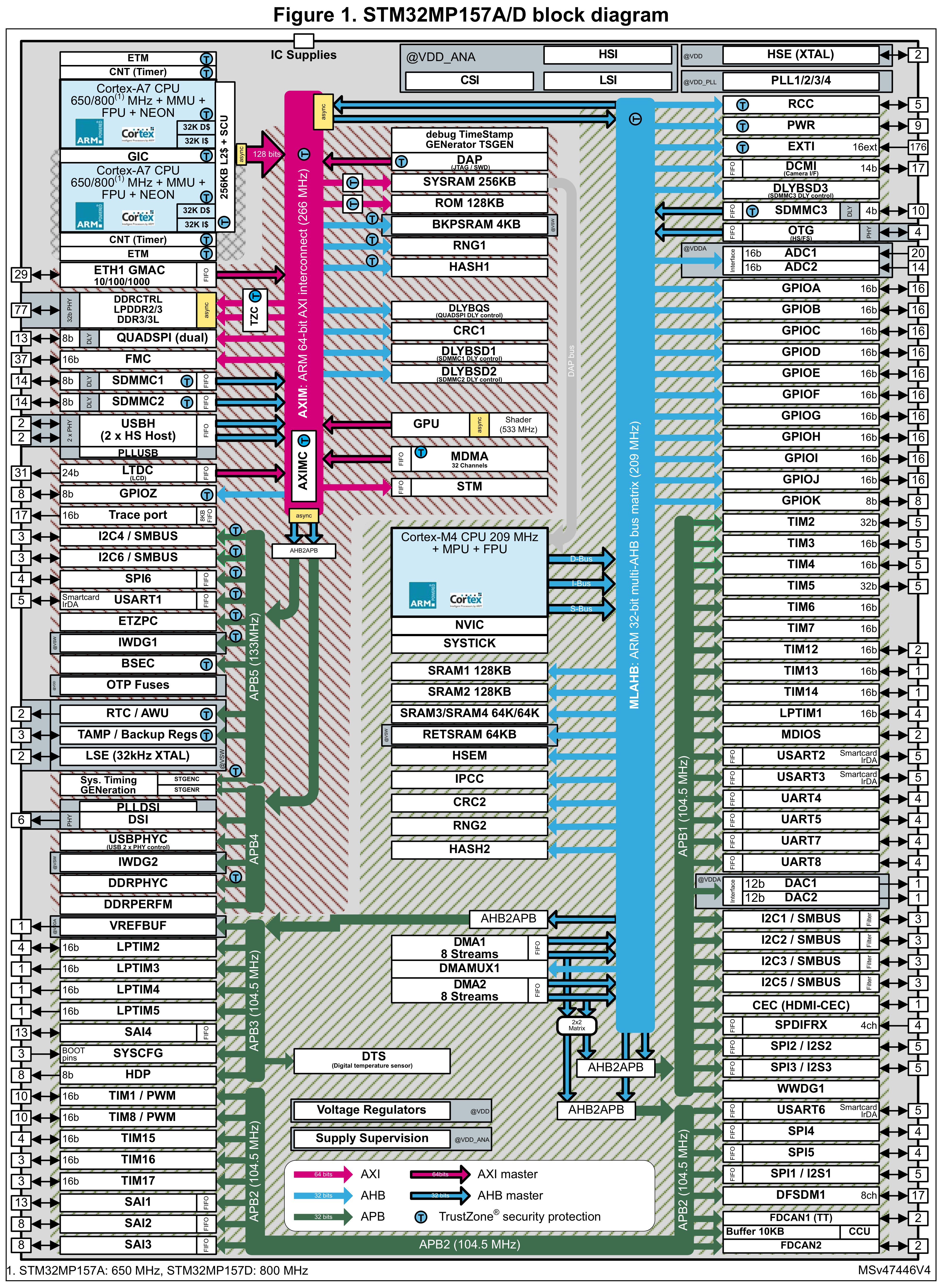

STM32MP157是一款双核主处理器+实时协处理器的soc,主处理器采用ARM Cortex-A7,频率可达650MHz, 实时协处理器采用Cortex-M4,频率可达209Mhz。最大支持1GByte的DDR3/3L, 具有千兆以太网,最大1366×768分辨率的显示输出,Vivante GPU,Audio,USB,CAN,时钟,SPI等等外设。

STM32MP157相较于STM32其他系列要复杂得多

除了Cortex-A7 以及Cortex-M4之外的部件被称为核外外设或片上外设。 如GPIO、USART(串口)、I2C、SPI等都叫做片上外设。具体见 外设。

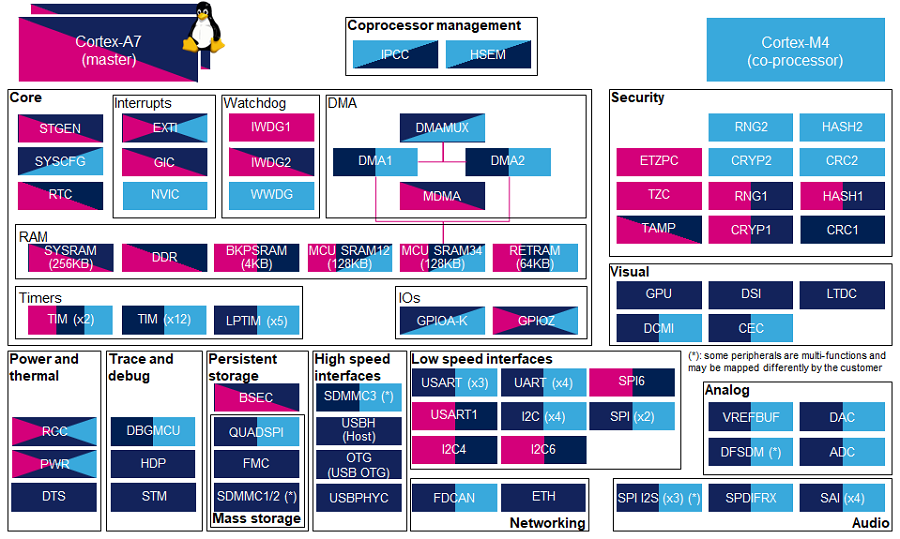

将上图的主要功能可以归类为: Cortex A7内核、Cortex M4核的协处理器、总线、易失性存储、 可持久性存储、时钟、定时器、电源管理、高速通信、低速通信、网络、多媒体、 模拟信号处理、LCD控制器、安全和IO输入输出等。

所以的外设都运行在以下三种环境中:

Cortex-A7安全环境

Cortex-A7非安全环境(主要运行Linux)

Cortex-M4

大多数的外设都只能处于一种环境内工作,例如当ADC设置为在Cortex-M4下运行, 那么Cortex-M4内核就独占了ADC的外设,在Cortex-A7内核下就不能对该外设进行控制。

有一小部分外设是不同内核独有的,如GIC是Cortex-A系列内核中用于中断控制,那么Cortex-M就不能去控制它, 同样NVIC是Cortex-M系统下的中断控制器,Cortex-A并不能去控制。

还有一小部分的外设可以在A7与M4之间共享,如GPIO控制。

具体的外设情况能配置为那种模式下,如下图所示

详细的介绍可以到官方wiki中查看 https://wiki.st.com/stm32mpu/wiki/STM32MP15_peripherals_overview

3.2. STM32MP157内部RAM¶

3.3. 存储器映射¶

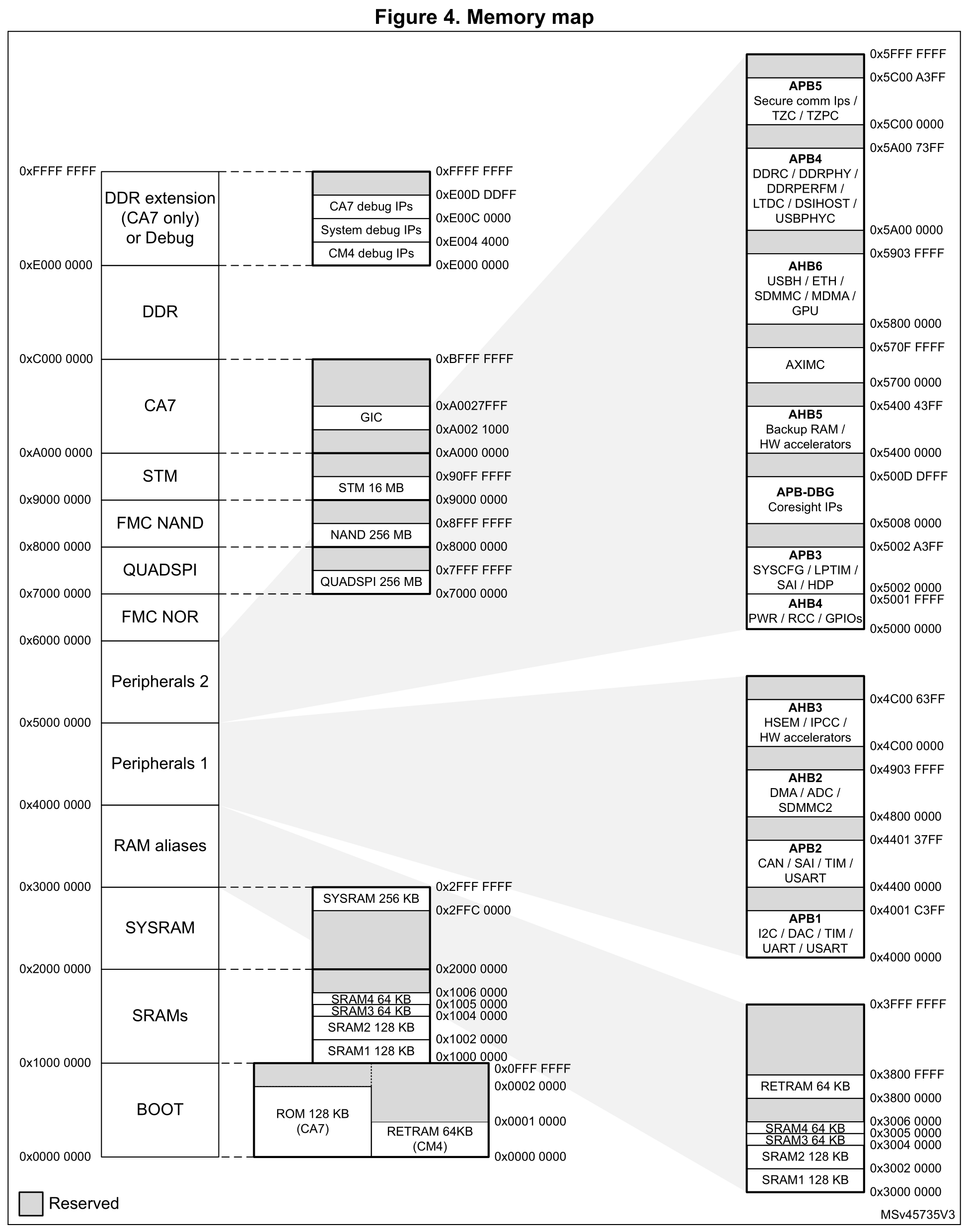

在 STM32MP157存储器映射 中,连接被控总线的是RAM和片上外设,这些功能部件共同排列在一个4GB的地址空间内。 我们在编程的时候,操作的也正是这些功能部件。

3.3.1. 存储器映射关系¶

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射,如下图所示, 如果给存储器再分配一个地址就叫存储器重映射。

图 5‑5 存储器映射(摘自参考手册-2.5 Memory organization)

3.3.2. 存储器区域功能划分¶

在这4GB的地址空间中,分成了13块不同的区域空间,每个块也都规定了用途。 每块的大小都至少有256MB,显然这是非常大的,芯片厂商在每个块的范围内设计各具特色的外设时并不一定都用得完, 都是只用了其中的一部分而已。

SRAMs、SYSRAM用于设计片内的SRAM。 地址空间0xFFC 0000 - 0x2FFF FFFF 总共256K的SRAM是A7专用的SYSRAM, 用于系统引导启动时使用。 在SRAMs区域块中,其中SRAM1,2,4都cortex M4独享的,SRAM3由A7和M4共享,作为共享的存储介绍。

表格 5-1 存储器SRAMs 内部区域功能划分

块 |

用途说明 |

地址范围 |

|---|---|---|

SRAMs |

SRAM1 128KB |

0x1000 0000 ~ 0x1001 FFFF |

SRAM2 128KB |

0x1002 0000 ~ 0x1003 FFFF |

|

SRAM3 64KB |

0x1004 0000 ~ 0x1004 FFFF |

|

SRAM4 64KB |

0x1005 0000 ~ 0x1005 FFFF |

从存储器映射图中我们并没看到可以固件烧写的flash区块,这就意味着 我们生成的M4固件并不能直接烧写到STM32MP157中,而是被加载到SRAMs区域块中去运行, 这块区域就得包含了代码的数据段、代码段等相关存储。