5. 时序分析理论基础¶

时序分析在FPGA规范的设计中是必要的,在FPGA高速系统的设计中更是必不可少,否则就会出现RTL逻辑仿真完全正确,而在下板验证时却因为时序不满足要求而使整个系统不能正常工作。在数字IC的设计中时序分析更是非常重要的一环。

时序分析的方法主要有两种,一种是静态时序分析,另一种是动态时序分析。静态时序分析是通过我们设计好电路中的已知参数利用EDA工具提供的模型分析出时钟和数据的关系。而动态时序分析是把设计好电路中的所有延时都考虑进来,在EDA仿真工具中把延时参数都加上,然后观察仿真的波形并测量Ts(建立时间:采样时钟的上 升沿到达数据起始位置的时间)、Th(保持时间:采样时钟的上升沿到达数据结束位置的时间)是否满足时序的要求,需要电路模拟跑起来。静态时序分析是一个很常用且快捷高效的时序分析方法,所以我们先从静态时序分析的通用模型讲起。

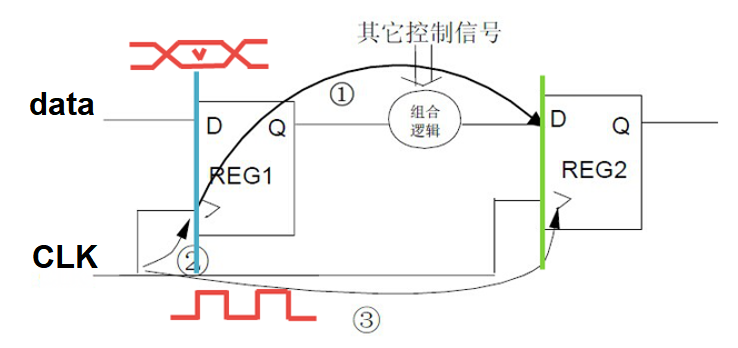

如图 57‑1所示时序分析需要关心的路径有以下几点:

(1)从输入到输出的路径;

(2)从输入到寄存器的路径;

(3)从寄存器到输出的路径;

(4)从寄存器到寄存器的路径;

(5)异步清零信号和时钟存在异步的进入和退出的时序问题。

其中寄存器到寄存器之间的路径分析占整个时序分析的60%以上,也是本题目所要分析的内容。

图 57‑1

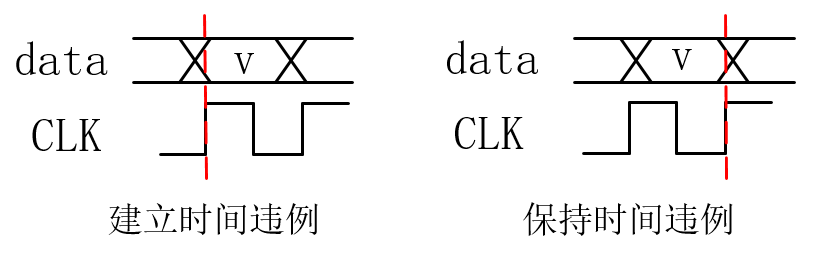

时序分析问题是如何引入的呢?我们以寄存器到寄存器之间的路径分析为例,如图 57‑2所示,时钟的上升沿在寄存器REG1的时钟端和数据稳定时在寄存器REG1的D端在图中蓝色竖线的位置是同时进行的,但数据要从图中①所示的数据路径传到寄存器REG2的D端,而时钟则从图中③所示的路径到达寄存器REG2的时钟端 ,也就是说数据和时钟所经过的路径是不同的,这会使数据和时钟到达图中绿色竖线的位置,即寄存器REG2的D端和时钟端的相位关系发生变化,在某些情况下会导致刚好如图 57‑3所示的情况,即时钟在数据不稳定的情况下对数据进行了采样,这会产生亚稳态现象,导致我们采集到数据是错误的。我们做时序约束的目的就是要解决这种问题,让时钟采集到稳定的数据。

图 57‑2

图 57‑3

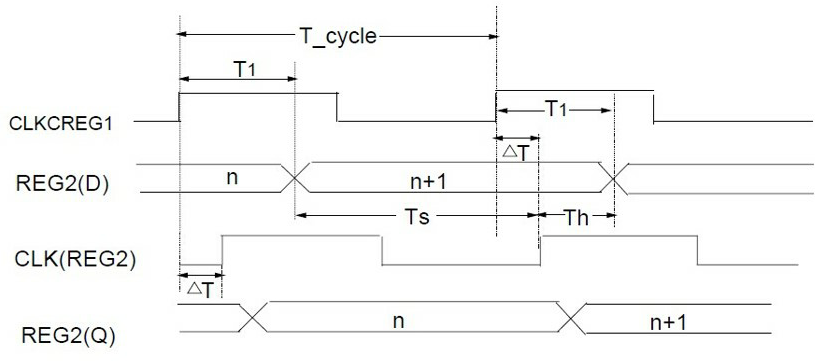

如图 57‑4所示,我们用波形的方式来描述这一问题。

图 57‑4

图 57‑4中的T1为数据路径的延迟,等于图 57‑2中①所示的路径,它包括寄存器REG1时钟端到寄存器REG1数据输出端Q的延迟为Tco与两级寄存器之间的组合逻辑与布线延迟Tdata之和。

图 57‑4中的△T为时钟偏斜,等于图 57‑2中时钟到第二级寄存器时钟端的延迟为T③与时钟到第一级寄存器的时钟端的延迟T②之差。注:△T的值可以为正值也可以为负值,一般情况下T③的值会大于T②的值,这样它们之间的差就为一个正值,更容易计算。

另外图 57‑4中的Ts为建立时间,Th为保持时间,T_cycle为时钟周期

根据波形图所表示的内容可以得出建立保持时间公式的推导,如下所示:

建立时间的公式为:Ts = T_cycle – T1 + △T = T_cycle –(Tco + Tdata)+ △T

保持时间的公式为:T1 – △T = (Tco + Tdata)– △T

上面的公式推导是在理想环境下的设定,否则还需要加入T_setup(建立时间的门限)和T_hold(保持时间的门限)这两个参量。T_setup:时钟沿来到之前数据必须保持稳定的最小时间,芯片选定即决定,和制作工艺有关。T_hold:时钟沿来到之后数据必须保持稳定的最小时间,芯片选定即决定,和制作工艺有 关。

然后将这两个参量和上面求得的建立时间和保持时间公式一起求出Sslack(建立时间的余量,由建立时间减去建立时间的门限得出)和Hslack(保持时间的余量,由保持时间减去保持时间的门限得出),要求Sslack和Hslack的值都要大于零。最后的公式为:

Sslack(建立时间的余量)≥ 0

= Ts–T_setup ≥ 0

= [T_cycle –(Tco + Tdata)+ △T] – T_setup ≥ 0

Hslack(保持时间的余量)≥ 0

= Th–T_hold ≥ 0

= [(Tco + Tdata)– △T] – T_hold ≥ 0

以上的分析是基于通用理论模型,也是其中一种静态时序分析的计算方法,有时候大家还会看到另一种静态时序分析的计算方法,很多学习者会将这两种分析方法搞混,这次我们将其一网打尽。下面的计算推导过程也是Quartus软件中自带的时序分析工具常用的方法,我们需要新引入一个概念,图 57‑5所示:

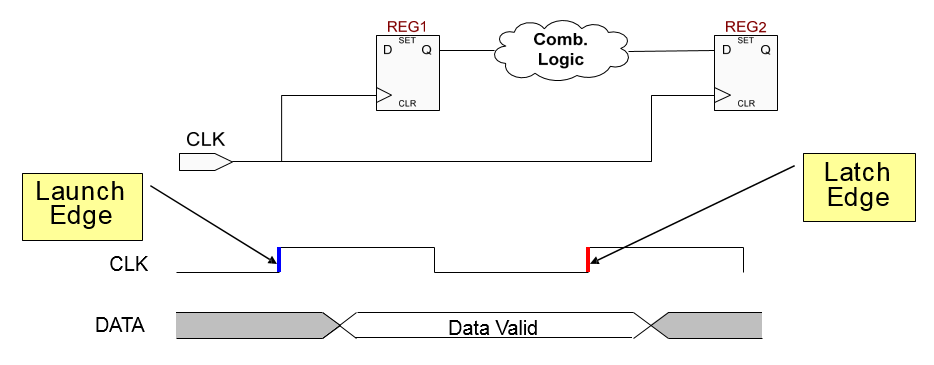

(1)Launch Edge(发射数据的沿):管脚传进来同步于数据的时钟的沿,也被认为是0时刻。

(2)Latch Edge(锁存数据的沿):目的地寄存器REG2锁存数据的沿,相对于发射沿延后1个时钟周期后的起始位置。

图 57‑5

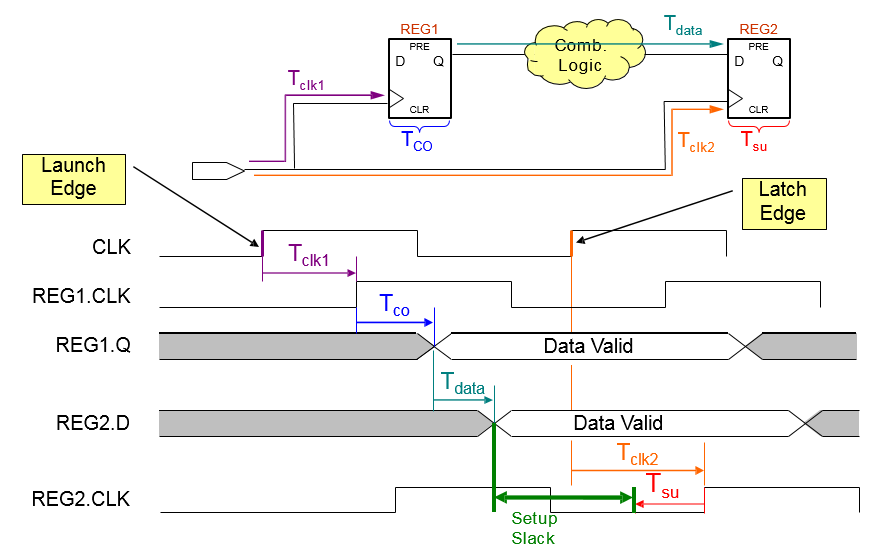

如图 57‑6所示,我们引入数据到达寄存器的时间Data Arrival Time,就是说数据从Launch Edge开始到寄存器REG2的D端所用的时间:

(1)建立时间的Data Arrival Time(当前数据开始到达的时间)= launch edge + Tclk1 + Tco + Tdata

(2)保持时间的Data Arrival Time(当前数据结束到达的时间,也是下一个数据开始到达的时间)= next launch edge + Tclk1 + Tco + Tdata

图 57‑6

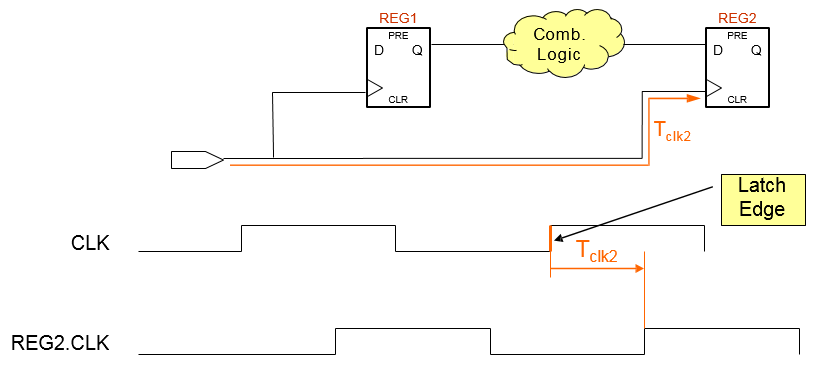

如图 57‑7所示,为我们采样时钟到达的时间Clock Arrival Time,就是说时钟从Latch Edge到寄存器REG2的时钟端所用的时间:Clock Arrival Time = latch edge + Tclk2

图 57‑7

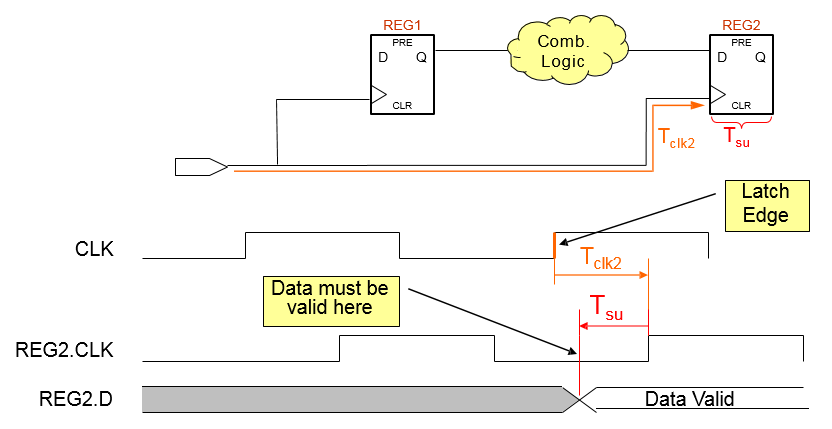

如图 57‑8所示为建立时间数据要求达到的时间Data Required Time,我们可以理解为时钟和数据在到达寄存器REG1时之间的相对位置是固定的,但时钟和数据分别走了不同的路径到达寄存器REG2,而我们希望时钟和数据到达寄存器REG2时能够继续保持之前的相对位置。数据实际到达的时间Data Arrival Time是已经确定的,为了使时钟和数据在到达寄存器REG2时继续保持原来的相对位置,就需要时钟的相对位置匹配数据,同时还需要预留出寄存器REG2的建立时间门限,所以要求时钟到达的时间为:时钟实际到达寄存器REG2的时间(Clock Arrival Time)– 寄存器REG2的建立时间门限(Tsu),得到的结果就是时钟所经过的路径,也可以将其理解为就是满足建立时间数据要求达到的时间,公式为:Data Required Time = Clock Arrival Time–Tsu

图 57‑8

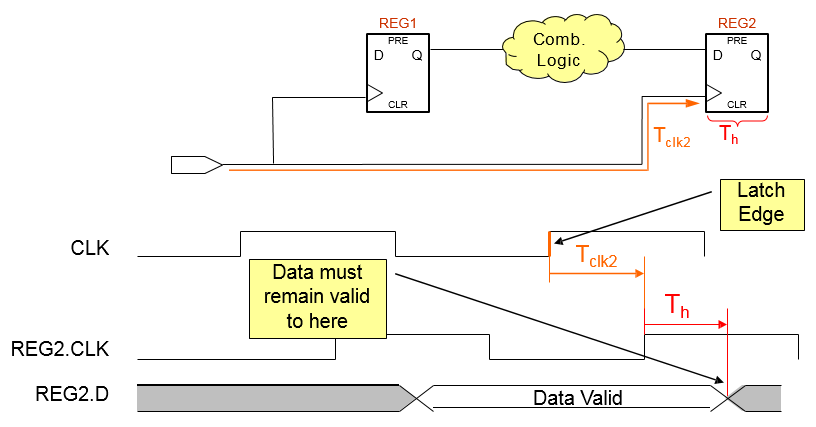

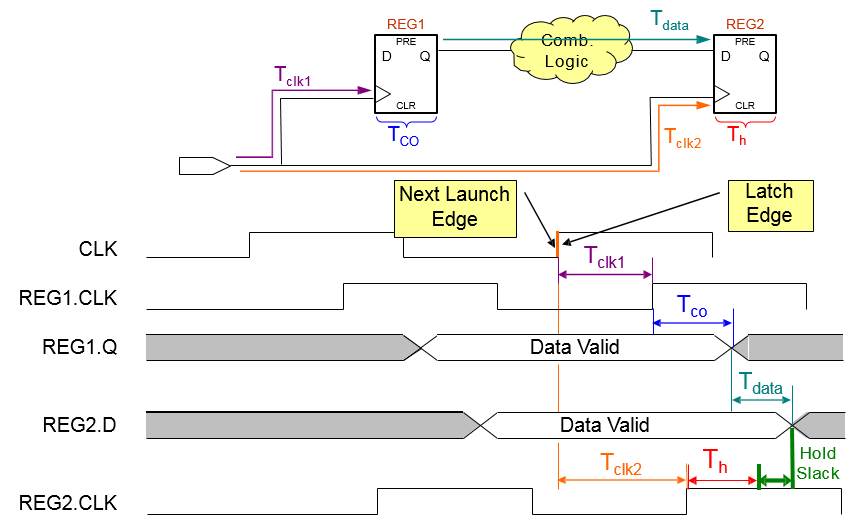

如图 57‑9所示为保持时间数据要求达到的时间Data Required Time,我们可以理解为时钟和数据在到达寄存器REG1时之间的相对位置是固定的,但时钟和数据分别走了不同的路径到达寄存器REG2,而我们希望时钟和数据到达寄存器REG2时能够继续保持之前的相对位置。数据实际到达的时间Data Arrival Time是已经确定的,为了使时钟和数据在到达寄存器REG2时继续保持原来的相对位置,就需要时钟的相对位置匹配数据,同时还需要预留出寄存器REG2的保持时间门限,所以要求时钟到达的时间为:时钟实际到达寄存器REG2的时间(Clock Arrival Time)+ 寄存器REG2的保持时间门限(Th),得到的结果就是时钟所经过的路径,也可以将其理解为就是满足保持时间数据要求达到的时间:Data Required Time = Clock Arrival Time + Th

图 57‑9

结合图 57‑10把上面分析得到的公式联合计算出Sslack(建立时间的余量),也就是数据到达寄存器REG2比时钟到达寄存器REG2提前的时间(算上寄存器REG2的建立时间),所以建立时间余量 = 时钟到达寄存器REG2的时间(数据要求达到的时间)–数据到达寄存器REG2端的时间(数据实际到达的时间),公式推导为:

Sslack(建立时间的余量)≥ 0

= Data Required Time–Data Arrival Time ≥ 0

=(Clock Arrival Time–Tsu)–(launch edge + Tclk1 + Tco + Tdata)≥ 0

=(latch edge + Tclk2–Tsu)–(launch edge + Tclk1 + Tco + Tdata)≥ 0

图 57‑10

结合图 57‑11计算出Hslack(保持时间的余量),也就是数据到达寄存器REG2(算上寄存器REG2的保持时间)比时钟到达寄存器REG2滞后的时间,所以保持时间余量 = 数据到达寄存器REG2端的时间(数据实际到达的时间)– 时钟到达寄存器REG2的时间(数据要求达到的时间),公式推导为:

Hslack(保持时间的余量)≥ 0

= Data Arrival Time–Data Required Time ≥ 0

=(next launch edge + Tclk1 + Tco + Tdata)–(Clock Arrival Time + Th)≥ 0

=(next launch edge + Tclk1 + Tco + Tdata)–(latch edge + Tclk2 + Th)≥ 0

图 57‑11

我们将上面推导的公式进行化简,具体如下:

(1)Sslack(建立时间的余量)≥ 0

= Data Required Time–Data Arrival Time ≥ 0

=(Clock Arrival Time–Tsu)–(launch edge + Tclk1 + Tco + Tdata)≥ 0

=(latch edge + Tclk2–Tsu)–(launch edge + Tclk1 + Tco + Tdata)≥ 0

= latch edge + Tclk2–Tsu–launch edge-Tclk1–Tco–Tdata ≥ 0

=(latch edge–launch edge)–(Tco + Tdata)+(Tclk2–Tclk1)-Tsu ≥ 0

=[T_cycle –(Tco+Tdata)+ △T] – Tsu ≥ 0和通用模型的公式一致

(2)Hslack(保持时间的余量)≥ 0

= Data Arrival Time–Data Required Time ≥ 0

=(next launch edge + Tclk1 + Tco + Tdata)–(Clock Arrival Time + Th)≥ 0

=(next launch edge + Tclk1 + Tco + Tdata)–(latch edge + Tclk2 + Th)≥ 0

= next launch edge + Tclk1 + Tco + Tdata–latch edge-Tclk2-Th ≥ 0

=(next launch edge–latch edge)+(Tco + Tdata)+(Tclk1-Tclk2)-Th ≥ 0

=[(Tco + Tdata)- △T] - Th ≥ 0和通用模型的公式一致

通过时序分析工具中的模型公式化简可以看出建立保持时间是否违例和Tclk1、Tclk2的时间长短无关,而与(Tclk2–Tclk1)的绝对值|△T|的值有关,还和采样时钟的频率、寄存器到寄存器之间的路径延迟有关。

以上的所有关于时序分析的计算在时序分析工具中都会给我们自动算好,其中还会加入时钟的不确定度和时钟的悲观度等参数信息。我们根据公式中参数和计算的结果就可以确定通过什么方式来优化才能使我们的时序达到最优。